Национальный исследовательский ядерный университет «МИФИ»

Институт интеллектуальных кибернетических систем

Кафедра №12 «Компьютерные системы и технологии»

Курсовой проект

"Проектирование процессора"

Студент:

Группа:

Преподаватель:

Литвинов В.А.

Б23-503

Ядыкин И.М.

Москва — 2025/2026

Проектирование блока операций

Примеры и алгоритмы выполнения операций

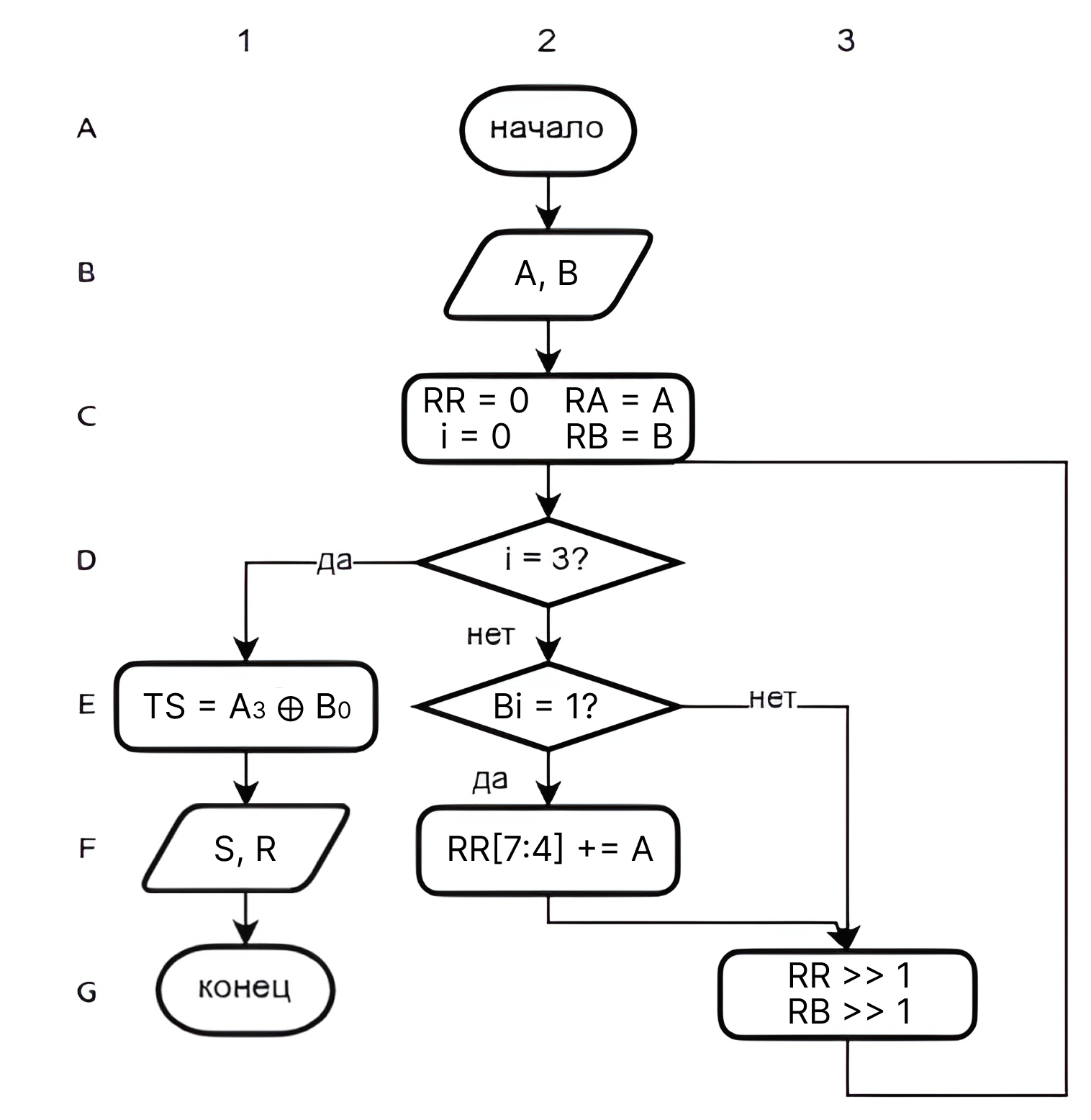

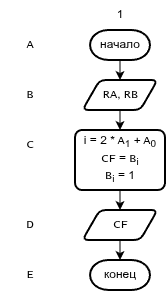

Алгоритм операции УМНОЖЕНИЕ

Умножение выполняется по алгоритму умножения с младших разрядов множителя и сдвигом

суммы частичных произведений вправо с одним корректирующим шагом. Данный алгоритм при

представлении сомножителей в прямом коде можно выразить следующей формулой:

$$[A]_{\text{п}} = a_3, a_2 a_1 a_0$$

$$[A]_{\text{п}} \cdot [B]_{\text{п}} = (..((0 + A \cdot b_0) \cdot p^{-1} + A \cdot b_1) \cdot p^{-1} + ... + A

\cdot b_{n-1}) \cdot p^{3}$$

Пример 1:

$[\mathrm{A}]_\mathrm{п} = 0.111 = 7$

$[\mathrm{B}]_\mathrm{п} = 0.111 = 7$

$\mathrm{Зн} = 0 \oplus 0 = 0$

$[\mathrm{A}*\mathrm{B}]_\mathrm{п} = 0.0110001 = 49$

Пример 2:

$[\mathrm{A}]_\mathrm{п} = 0.111 = 7$

$[\mathrm{B}]_\mathrm{п} = 1.101 = -5$

$\mathrm{Зн} = 1 \oplus 0 = 1$

$[\mathrm{A}*\mathrm{B}]_\mathrm{п} = 1.0100011 = -35$

Представим рассмотренный метод умножения в виде схемы алгоритма на рисунке

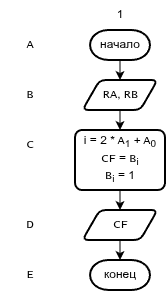

Проверка бита с установкой его в единицу

Операция проверяет бит в RB по адресу из RA, устанавливает флаг CF, если значение бита в операнде 1, значение

бита в операнде устанавливается в 1

Пример 1:

$RA = 0000$

$RB = 0001$

$CF = 1$

$RB = 0001$

Пример 2:

$RA = 0001$

$RB = 0001$

$CF = 0$

$RB = 0011$

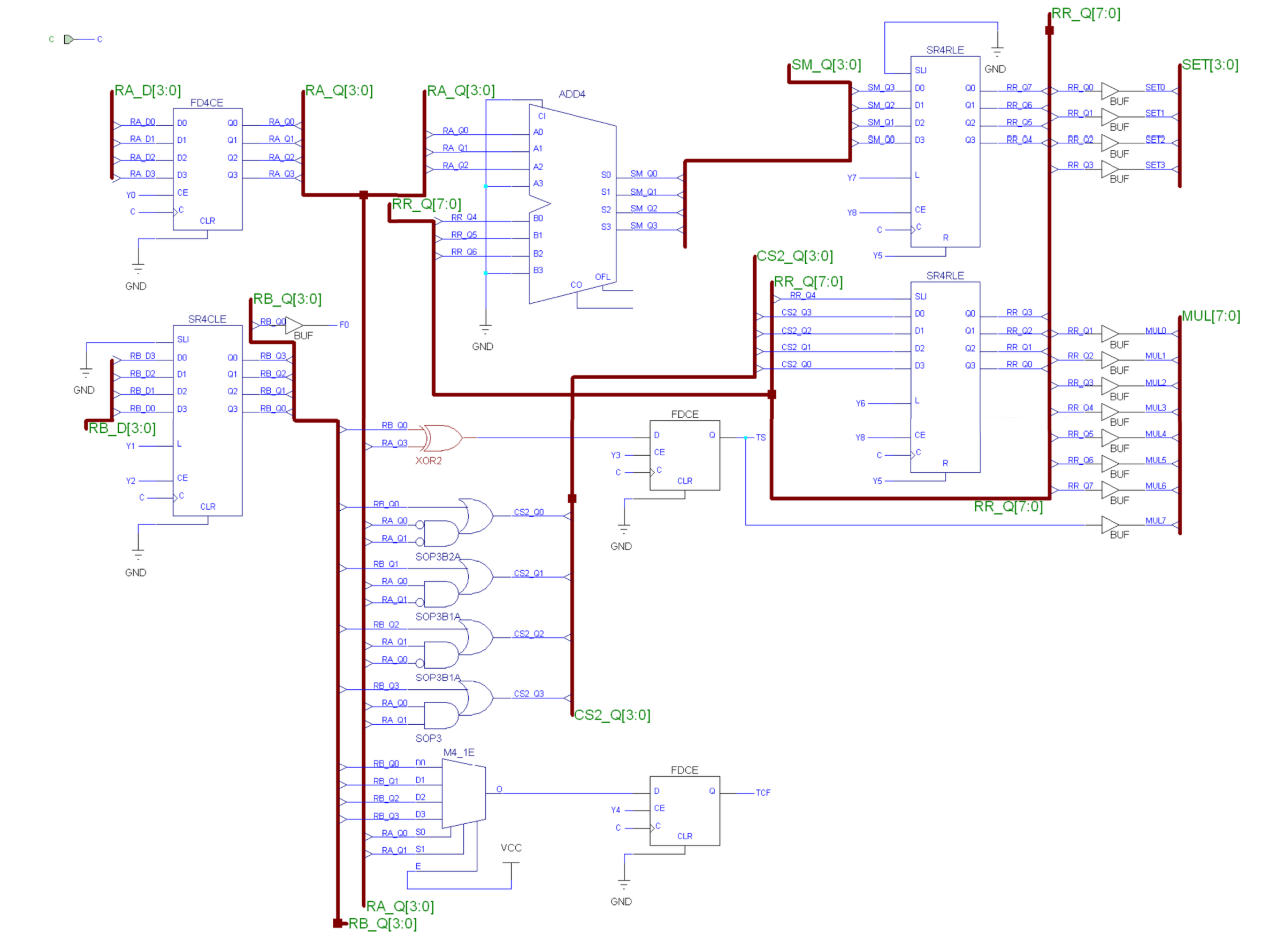

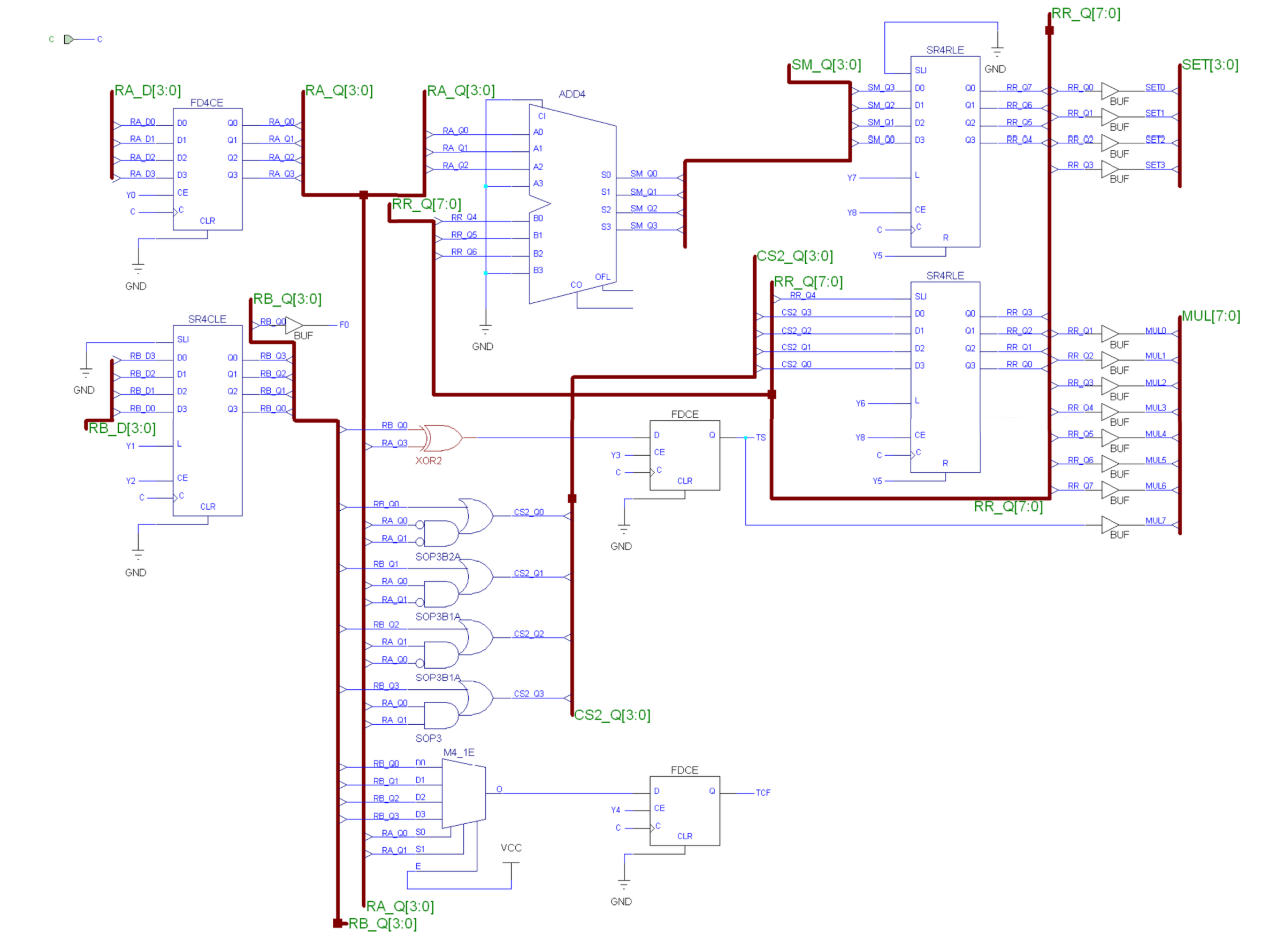

Функциональная схема блока операций

Функциональная схема блока операций представлена на рисунке , в таблице приведены все элементы функциональной схемы блока операций с их функциями и

назначением.

| Обозначение блока |

Назначение |

| RA |

Регистр первого операнда, 4 разряда, хранение, параллельная загрузка A |

| RB |

Регистр второго операнда, 4 разряда, хранение, параллельная загрузка B, логический сдвиг вправо,

формирование сигнала F0 |

| RLO |

Регистр младшей части результата, 4 разряда, хранение, параллельная загрузка, логический сдвиг вправо,

синхронный сброс в 0 |

| RHI |

Регистр старшей части результата, 4 разряда, хранение, параллельная загрузка, логический сдвиг вправо с

переносом в RLO, синхронный сброс в 0 |

| CS1 |

Формирование знака произведения |

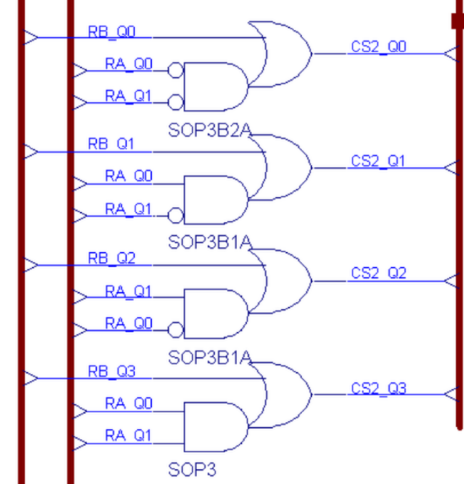

| CS2 |

Формирование нового значения B с установленным битом по индексу A |

| CS3 |

Формирование флага CF (значения бита из B по индексу A) |

| SM |

Сумматор, 4 разряда |

| TS |

Регистр знака произведения, 1 разряд, хранение, загрузка |

| TCF |

Регистр флага CF (значения бита из B по индексу A), 1 разряд, хранение, загрузка |

Проектирование логических элементов блока операций

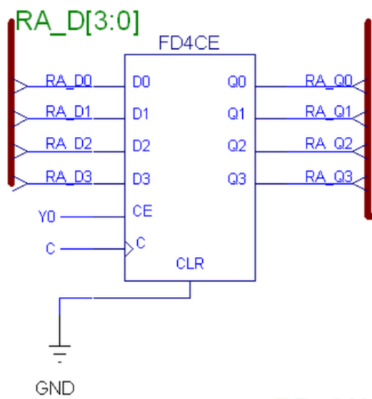

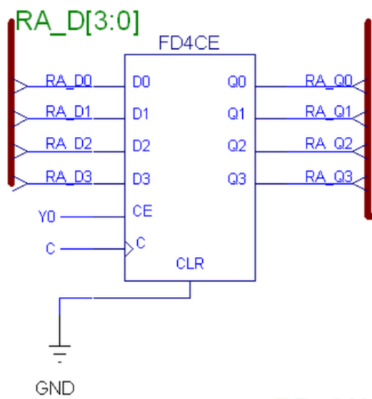

Регистр первого операнда RA

Данный регистр является четырёхразрядным регистром хранения. Наиболее подходящим для реализации функций регистра

RA является регистр FD4CE

| Обозначение |

Назначение |

| Y0 |

| 0 |

Хранение |

| 1 |

Параллельная загрузка |

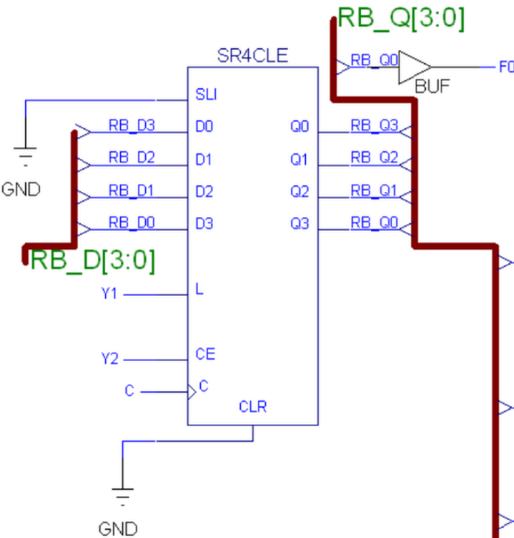

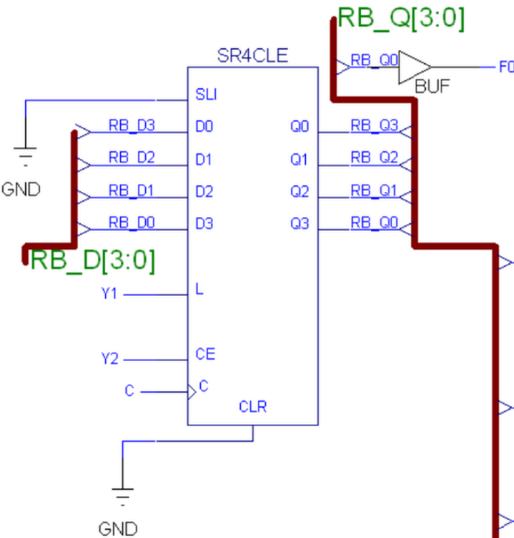

Регистр второго операнда RB

Данный регистр должен выполнять микрооперации хранения, параллельной загрузки и логического сдвига вправо. Для

реализации выбран универсальный регистр со сдвигом влево SR4CLE, для получения сдвига вправо входы и выходы

подключены в обратном порядке. Младший бит выхода Q0 формирует сигнал F0

| Обозначение |

Назначение |

| Y1 |

Y2 |

| 0 |

0 |

Хранение |

| 1 |

0 |

Параллельная загрузка |

| 0 |

1 |

Логический сдвиг вправо |

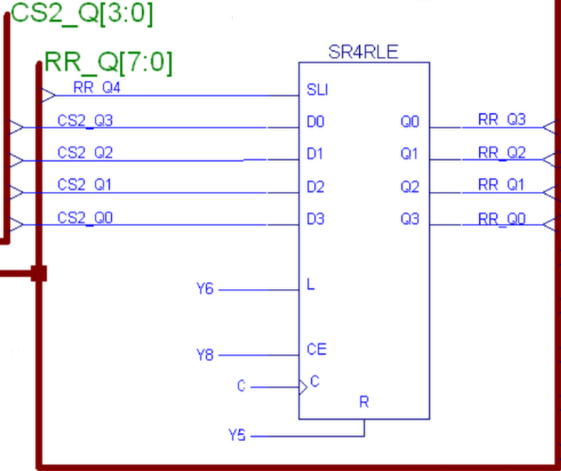

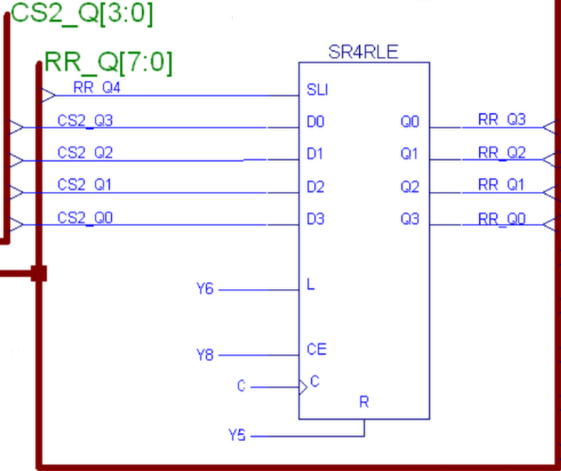

Регистр младшей части результата RLO

Данный регистр должен выполнять микрооперации хранения, параллельной загрузки, логического сдвига вправо (с

заполнением старшего бита младшим разрядом из RHI) и синхронного сброса в 0. Для реализации выбран универсальный

сдвиговый регистр SR4RLE

| Обозначение |

Назначение |

| Y5 |

Y6 |

Y8 |

| 0 |

0 |

0 |

Хранение |

| 0 |

1 |

0 |

Параллельная загрузка |

| 0 |

0 |

1 |

Логический сдвиг вправо |

| 1 |

0 |

0 |

Сброс в 0 |

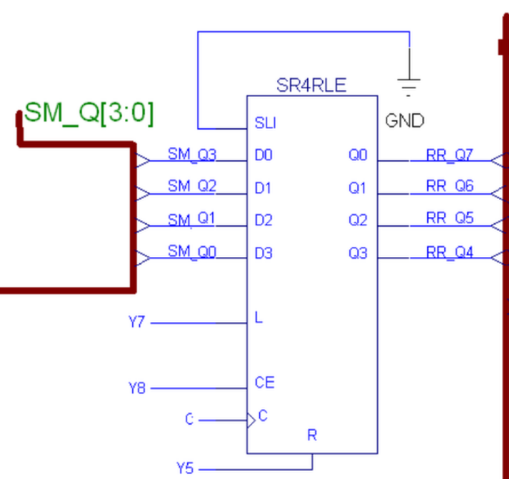

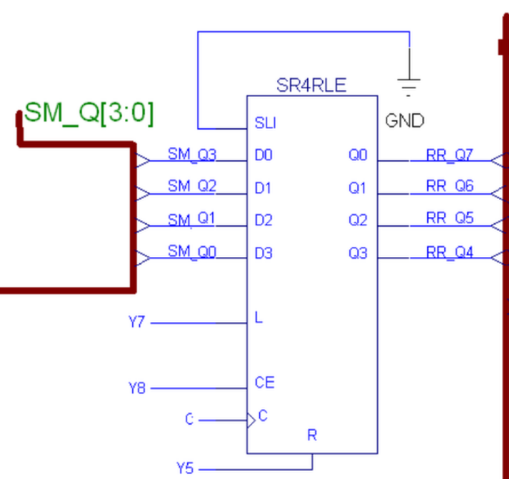

Регистр старшей части результата RHI

Данный регистр должен выполнять микрооперации хранения, параллельной загрузки, логического сдвига вправо (c

коммутацией младшего бита в старший разряд RLO) и синхронного сброса в 0. Для реализации выбран универсальный

сдвиговый регистр SR4RLE

| Обозначение |

Назначение |

| Y5 |

Y7 |

Y8 |

| 0 |

0 |

0 |

Хранение |

| 0 |

1 |

0 |

Параллельная загрузка |

| 0 |

0 |

1 |

Логический сдвиг вправо |

| 1 |

0 |

0 |

Сброс в 0 |

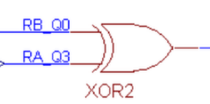

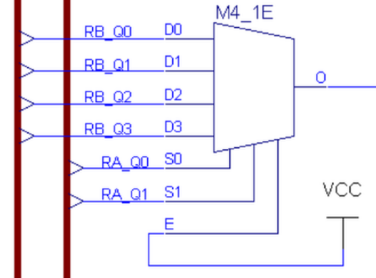

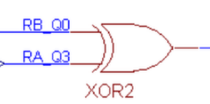

Комбинационная схема CS1

Отвечает за формирование знака произведения

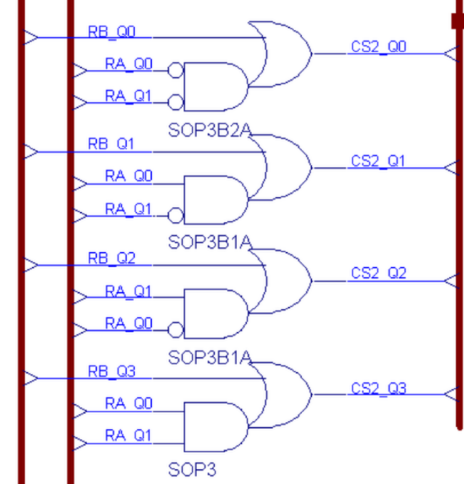

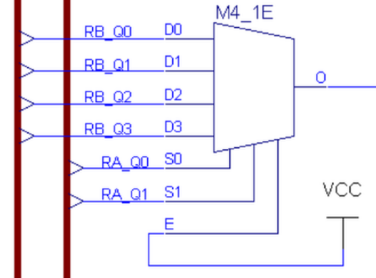

Комбинационная схема CS2

Отвечает за формирование нового значения B с установленным битом по индексу A

Комбинационная схема CS3

Отвечает за формирование флага CF (бита из B по индексу A)

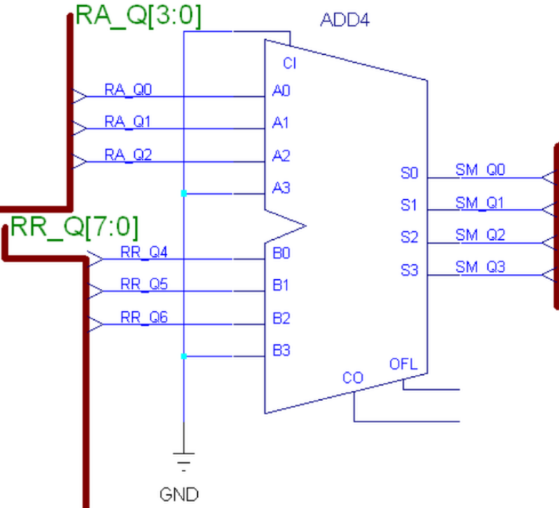

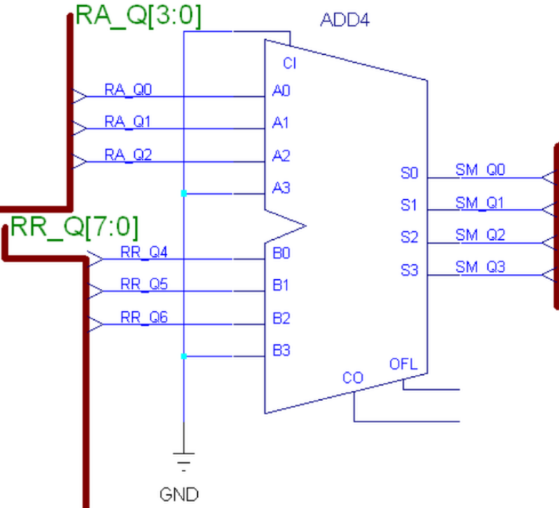

Сумматор SM

4-х битный сумматор ADD4

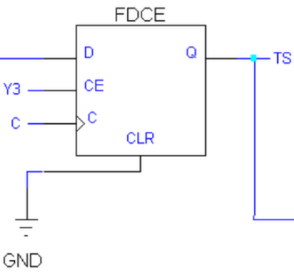

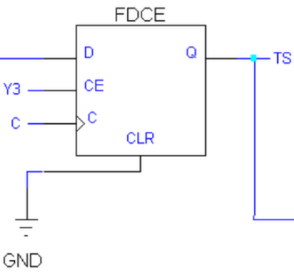

Регистр знака TS

| Обозначение |

Назначение |

| Y3 |

| 0 |

Хранение |

| 1 |

Загрузка |

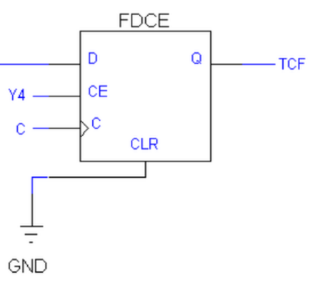

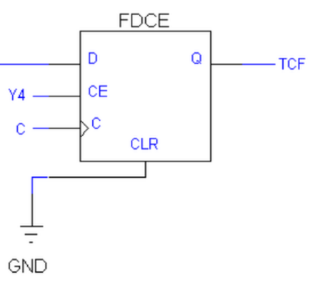

Регистр флага TCF

| Обозначение |

Назначение |

| Y4 |

| 0 |

Хранение |

| 1 |

Загрузка |

Логическая схема блока операций

Микропрограммы выполнения операций

Определение сигналов блока операций

| Сигнал |

Операция |

| Y0

| Загрузка A в RA |

| Y1 |

Загрузка B в RB |

| Y2 |

Логический сдвиг вправо RB |

| Y3 |

Загрузка значения на выходе CS1 в TS |

| Y4 |

Загрузка значения на выходе CS3 в TCF |

| Y5 |

Синхронный сброс RLO и RHI |

| Y6 |

Загрузка значения на выходе CS2 в RLO |

| Y7 |

Загрузка значения на выходе SM в RHI |

| Y8 |

Логический сдвиг вправо группы регистров RHI и RLO |

| Сигнал |

Операция |

| F0

| Младший разряд B |

Алгоритм микропрограммы УМНОЖЕНИЕ