Национальный исследовательский ядерный университет «МИФИ»

Институт интеллектуальных кибернетических систем

Кафедра №12 «Компьютерные системы и технологии»

Курсовой проект

"Проектирование процессора"

Студент:

Группа:

Преподаватель:

Литвинов В.А.

Б23-503

Ядыкин И.М.

Москва — 2025/2026

Проектирование блока операций

Формат данных

4-х разрядное слово представлено целыми числами с фиксированной запятой в прямом коде. Старший разряд отводится

под знак числа. Результат операции умножение - двойное слово, операции установки бита - одинарное слово.

$$[A]_{\text{п}} = a_3, a_2 a_1 a_0$$

$$[R]_{\text{п}} = r_7, r_6 r_5 r_4 r_3 r_2 r_1 r_0$$

Примеры и алгоритмы выполнения операций

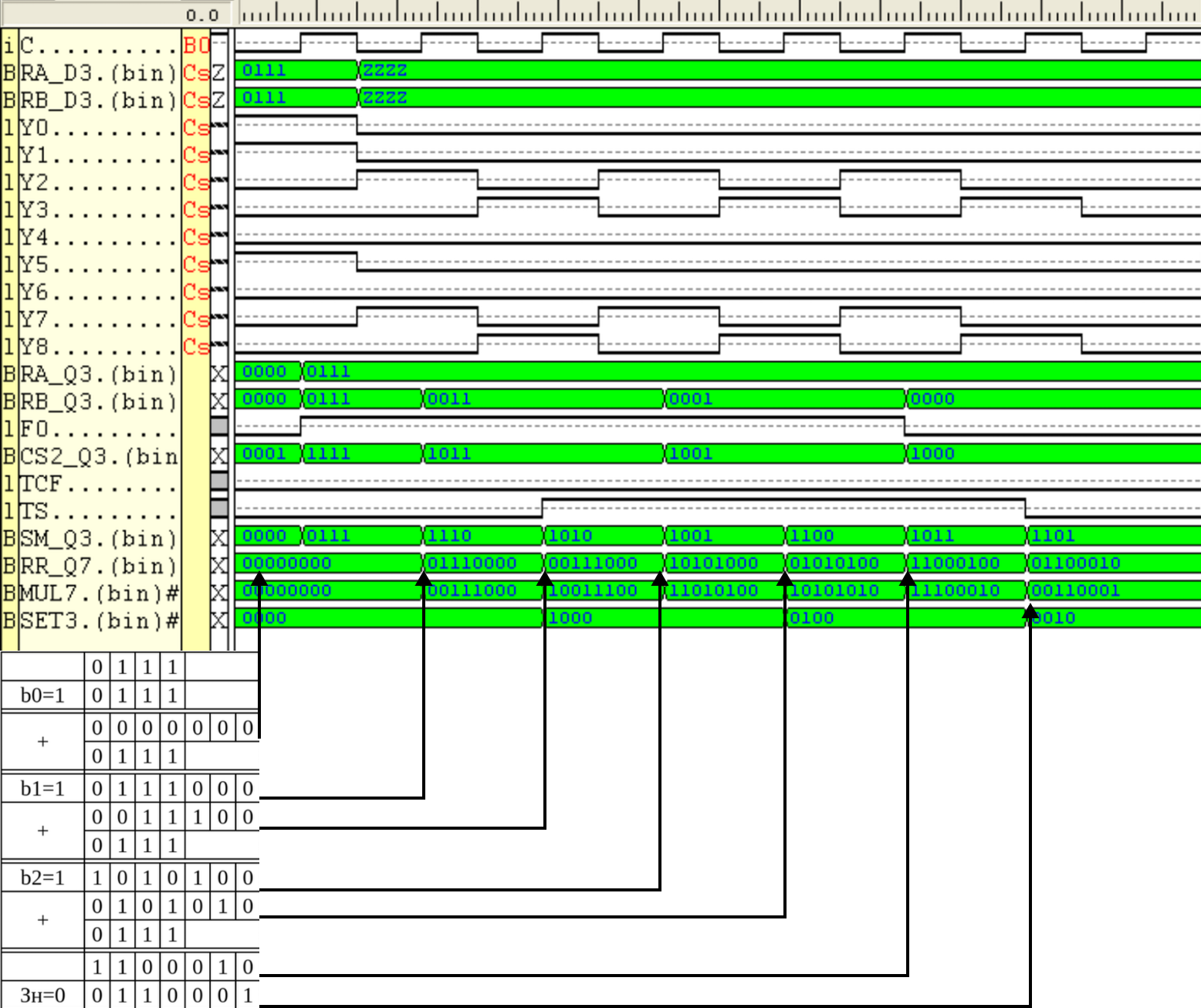

Алгоритм операции УМНОЖЕНИЕ

Умножение выполняется по алгоритму умножения с младших разрядов множителя и сдвигом

суммы частичных произведений вправо с одним корректирующим шагом. Данный алгоритм при

представлении сомножителей в прямом коде можно выразить следующей формулой:

$$[A]_{\text{п}} \cdot [B]_{\text{п}} = (..((0 + A \cdot b_0) \cdot p^{-1} + A \cdot b_1) \cdot p^{-1} + ... + A

\cdot b_{n-1}) \cdot p^{3}$$

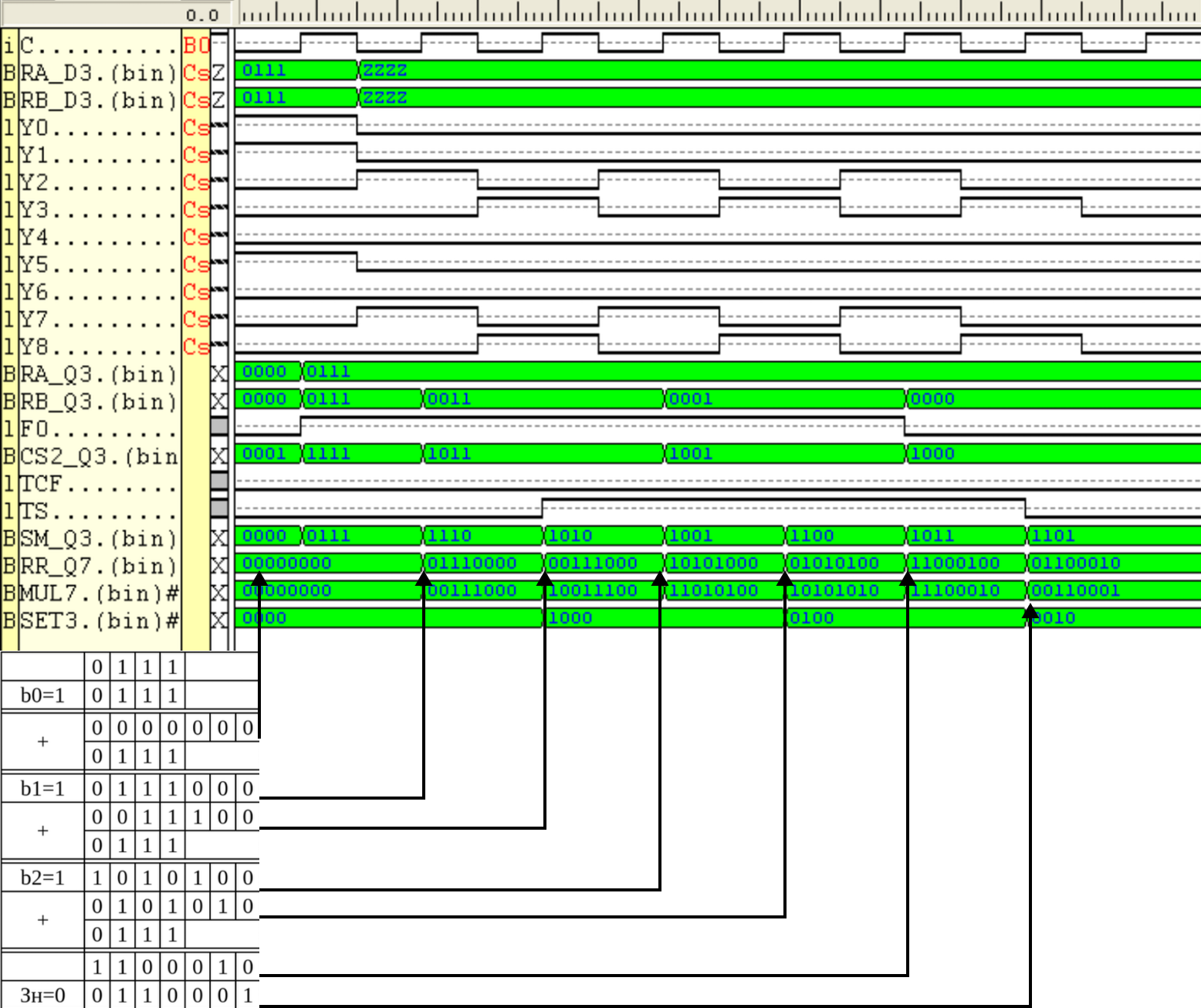

Пример 1:

$[\mathrm{A}]_\mathrm{п} = 0.111 = 7$

$[\mathrm{B}]_\mathrm{п} = 0.111 = 7$

$\mathrm{Зн} = 0 \oplus 0 = 0$

$[\mathrm{A} \cdot \mathrm{B}]_\mathrm{п} = 0.0110001 = 49$

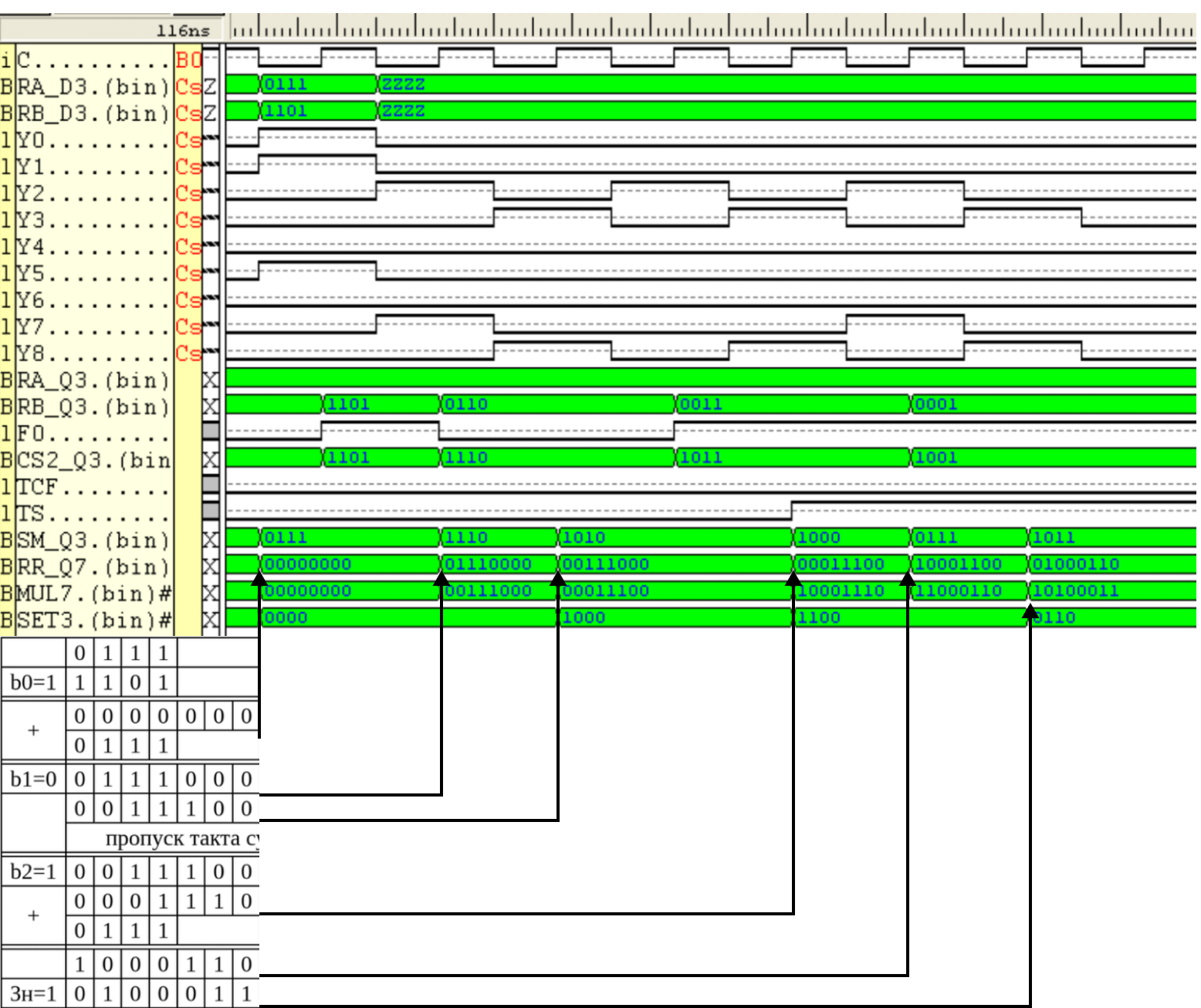

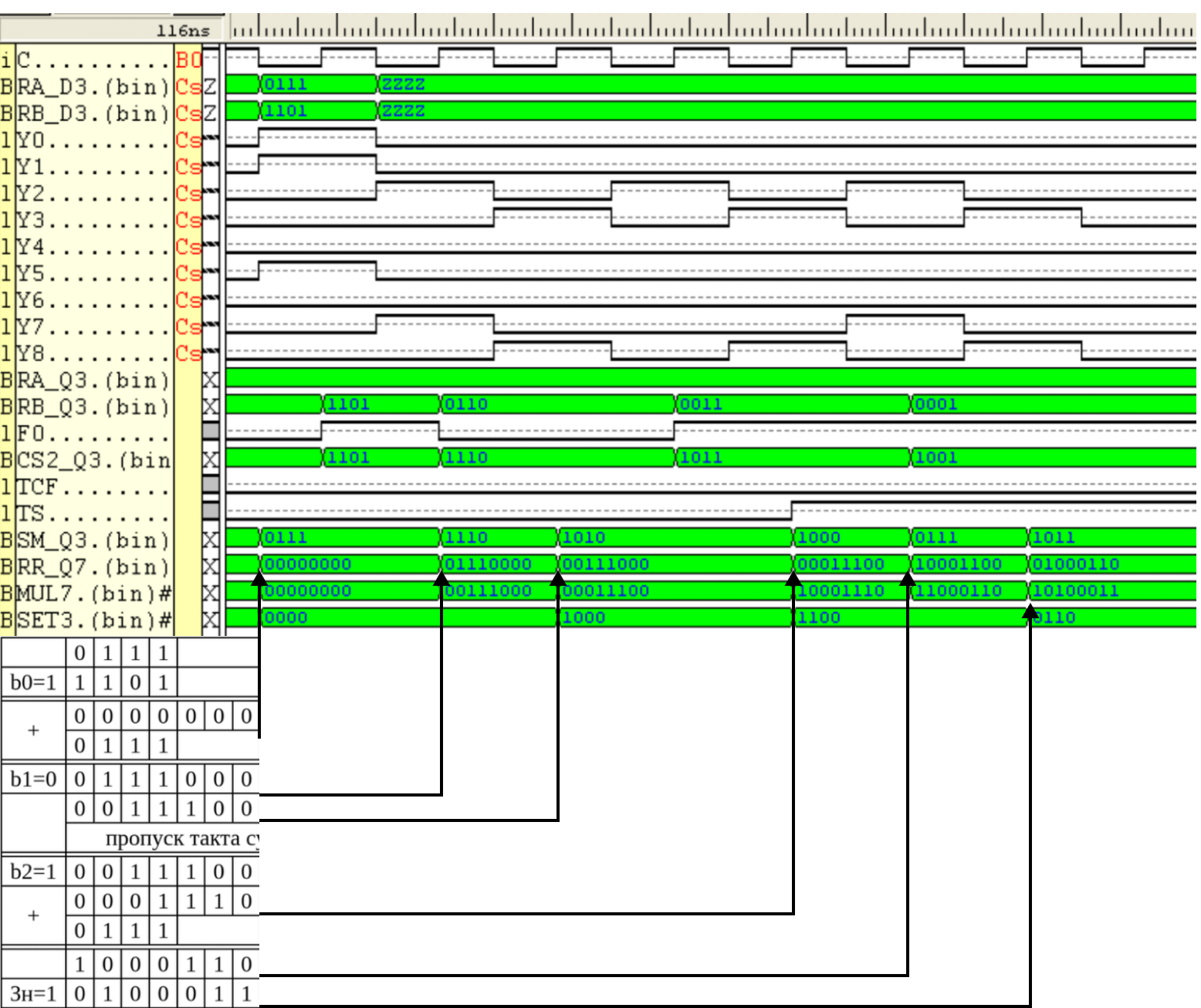

Пример 2:

$[\mathrm{A}]_\mathrm{п} = 0.111 = 7$

$[\mathrm{B}]_\mathrm{п} = 1.101 = -5$

$\mathrm{Зн} = 1 \oplus 0 = 1$

$[\mathrm{A} \cdot \mathrm{B}]_\mathrm{п} = 1.0100011 = -35$

TODO Рассмотренный алгоритм умножения представлен на рисунке .

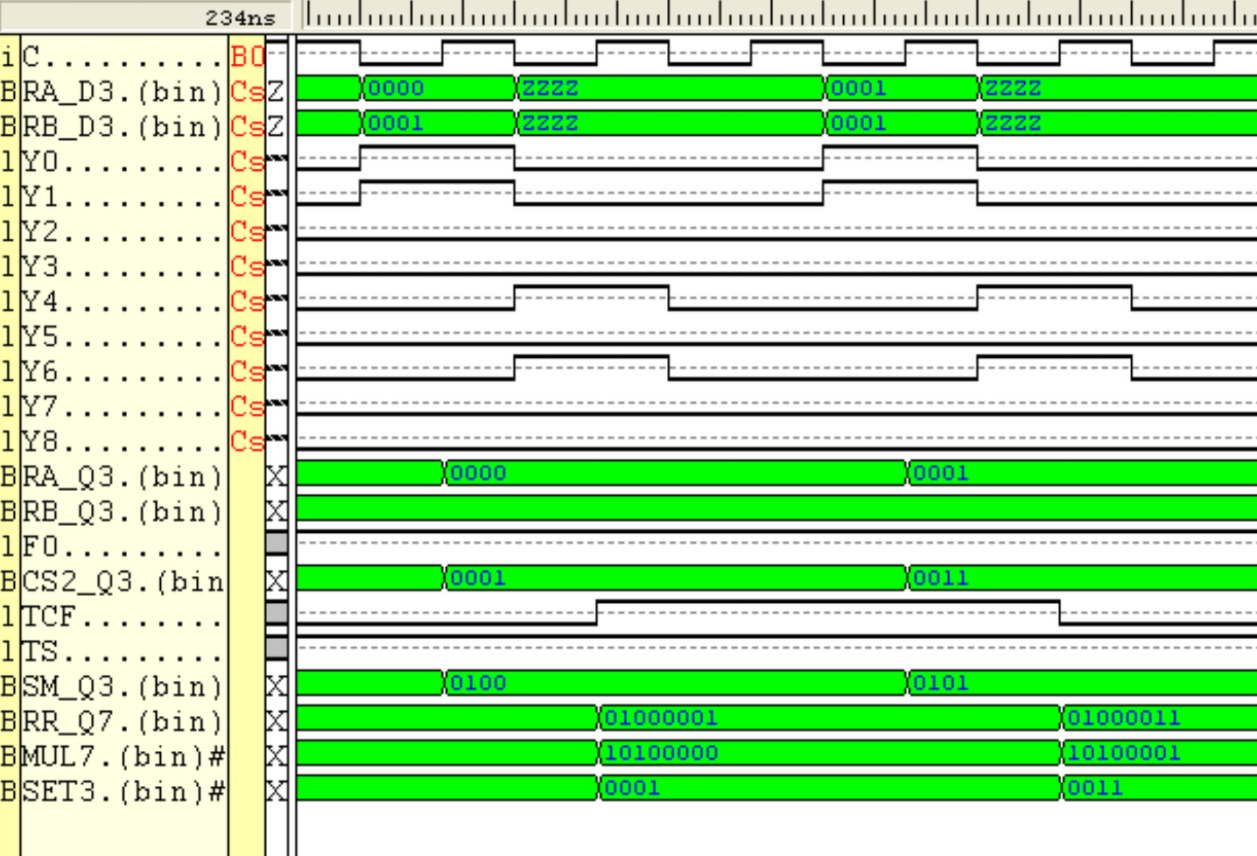

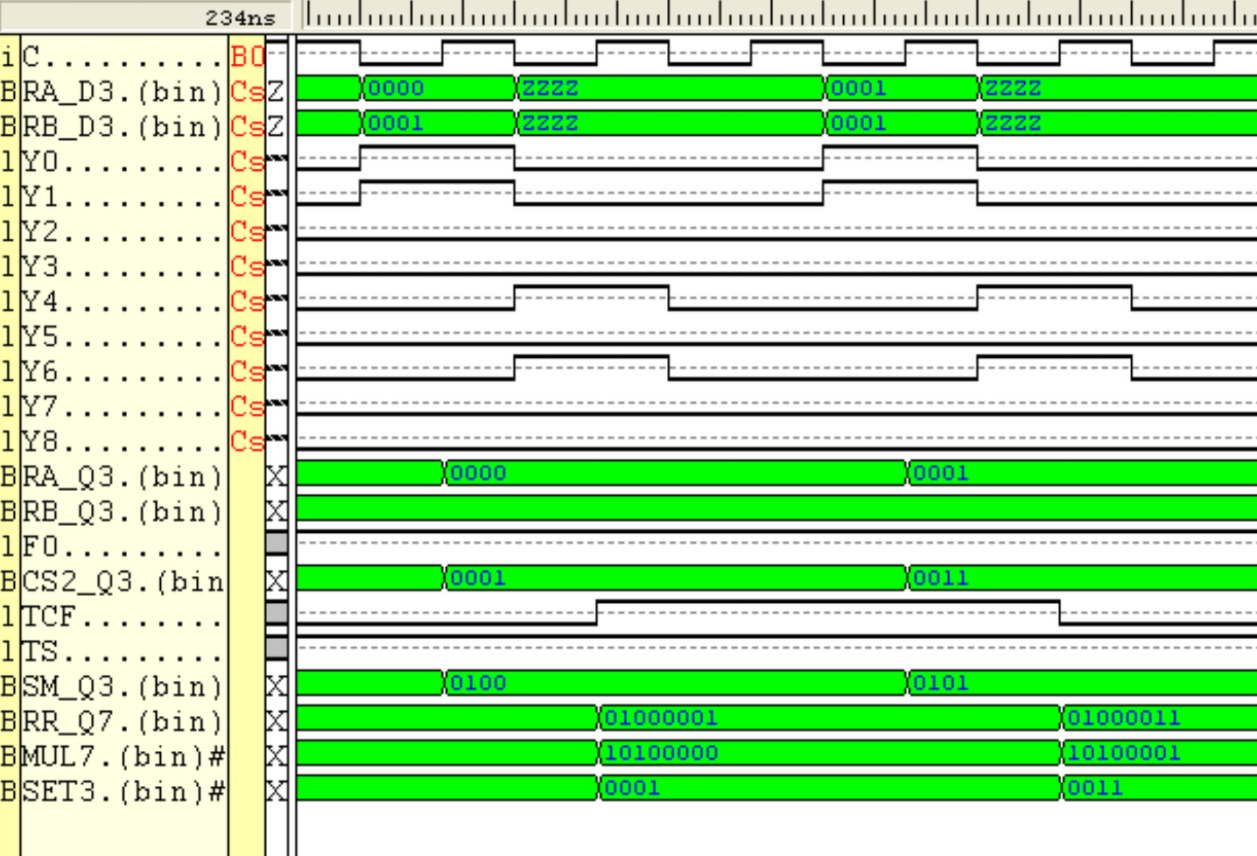

Проверка бита с установкой его в единицу

Операция проверяет бит в RB на позиции RA, устанавливает флаг CF, если значение бита в операнде 1, значение

бита в операнде устанавливается в 1.

Пример 1:

$A = 0000$

$B = 0001$

$-$

$i = 0$

$CF = RB_0 = 0$

$RB_0 = 1$

$RB = 0001$

Пример 2:

$A = 0001$

$B = 0001$

$-$

$i = 1$

$CF = RB_1 = 0$

$RB_1 = 1$

$RB = 0011$

TODO

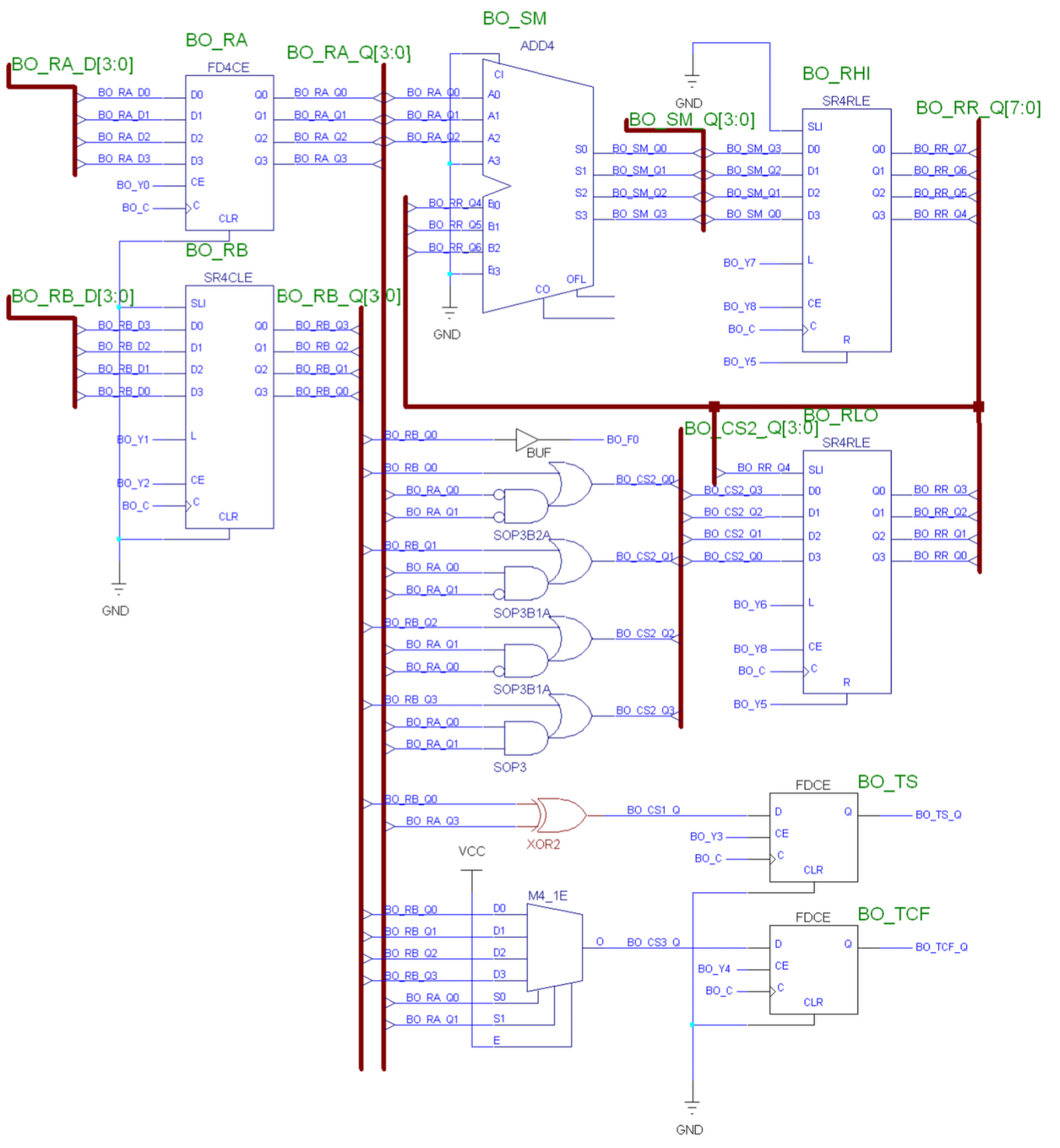

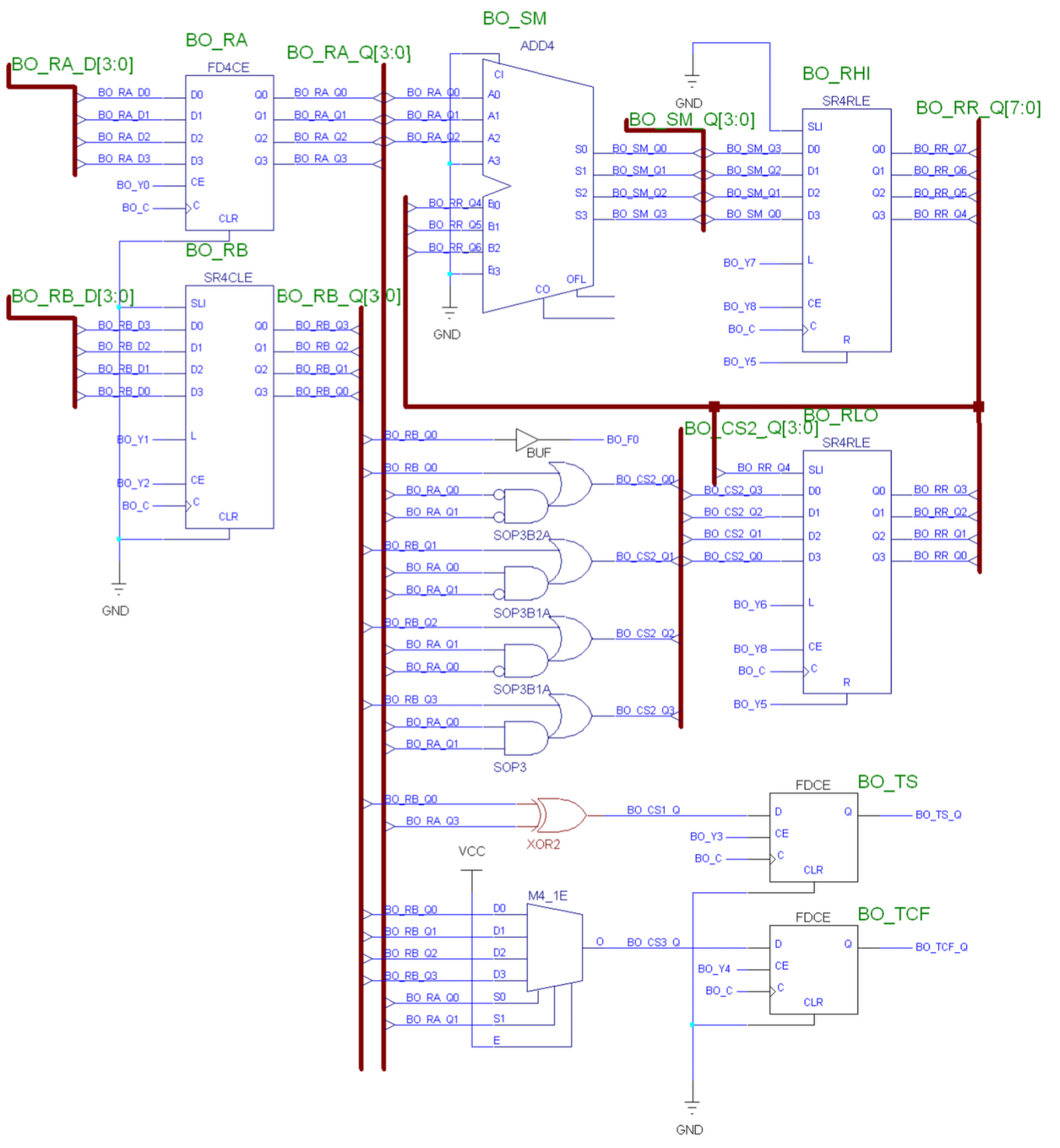

Функциональная схема блока операций

Функциональная схема блока операций представлена на рисунке , в таблице приведены все элементы функциональной схемы блока операций с их функциями и

назначением.

| Обозначение блока |

Назначение |

| RA |

Регистр первого операнда, 4 разряда, хранение, параллельная загрузка A |

| RB |

Регистр второго операнда / младшей части результата, 4 разряда, хранение, параллельная загрузка B,

логический сдвиг вправо, формирование сигнала F0 |

| RR |

Регистр старшей части результата, 4 разряда, хранение, параллельная загрузка, логический сдвиг вправо с

переносом в RB, синхронный сброс в 0 |

| CS1 |

Формирование знака произведения |

| CS2 |

Формирование флага CF (значения бита из B на позиции A) |

| CS3 |

Формирование нового значения B с установленным битом на позиции A |

| CS4 |

Выбор данных для загрузки в RB: B или CS3 |

| SM |

Сумматор, 4 разряда |

| TCF |

Регистр флага CF (значения бита из B на позиции A), 1 разряд, хранение, загрузка |

Проектирование логических элементов блока операций

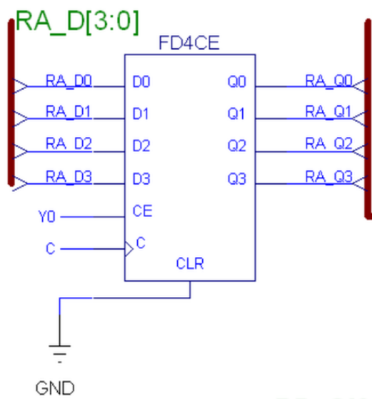

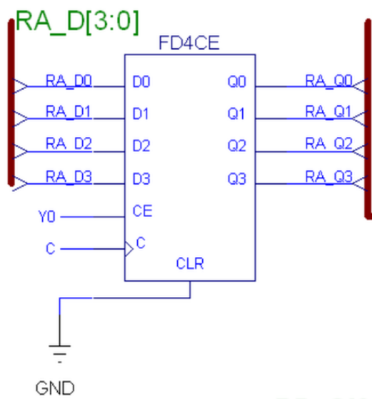

Регистр первого операнда RA

Данный регистр является четырёхразрядным регистром хранения. Наиболее подходящим для реализации функций регистра

RA является регистр FD4CE.

| Обозначение |

Назначение |

| Y1 |

| 0 |

Хранение |

| 1 |

Параллельная загрузка |

TODO

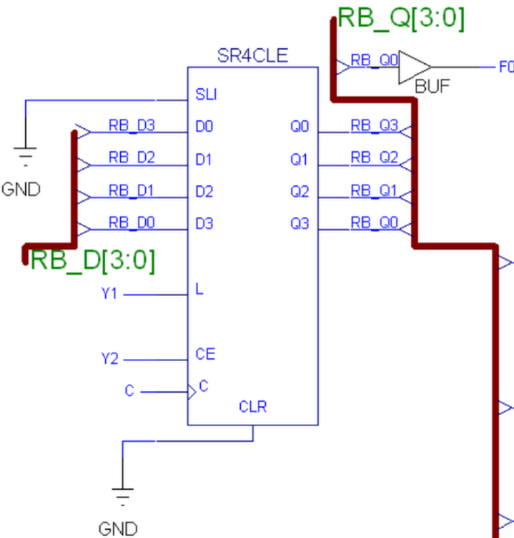

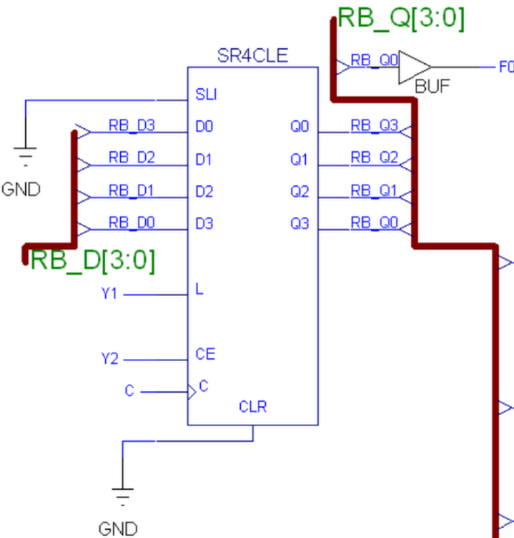

Регистр второго операнда / младшей части результата RB

Данный регистр должен выполнять микрооперации хранения, параллельной загрузки и логического сдвига вправо (с

заполнением старшего бита младшим разрядом из RR). Для

реализации выбран универсальный сдвиговый регистр SR4CLE. Младший бит выхода RB_Q0 формирует сигнал F0.

| Обозначение |

Назначение |

| Y2 |

Y3 |

| 0 |

0 |

Хранение |

| 1 |

0 |

Параллельная загрузка |

| 0 |

1 |

Логический сдвиг вправо |

TODO

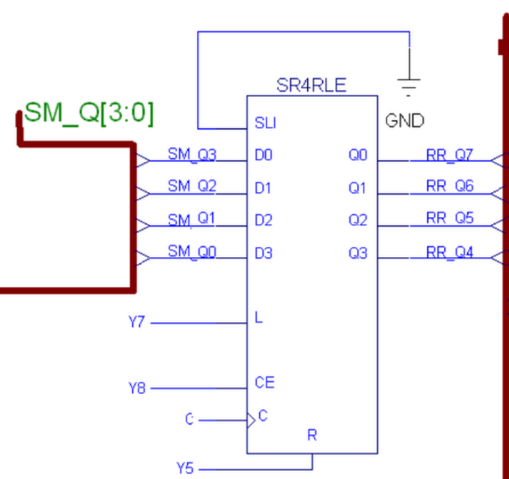

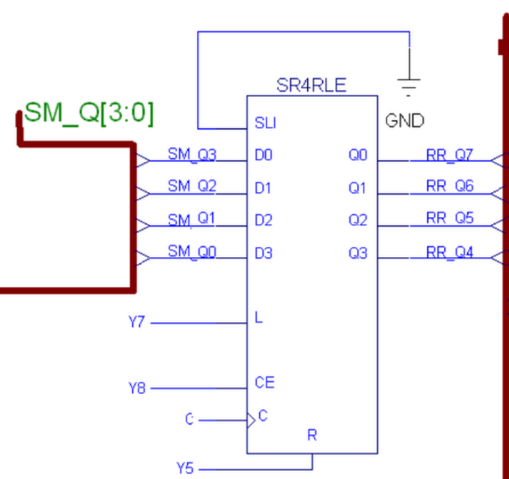

Регистр старшей части результата RR

Данный регистр должен выполнять микрооперации хранения, параллельной загрузки, логического сдвига вправо (c

коммутацией младшего бита в старший разряд RB) и синхронного сброса в 0. Для реализации выбран универсальный

сдвиговый регистр SR4RLE.

| Обозначение |

Назначение |

| Y4 |

Y5 |

Y6 |

| 0 |

0 |

0 |

Хранение |

| 1 |

0 |

0 |

Параллельная загрузка |

| 0 |

1 |

0 |

Логический сдвиг вправо |

| 0 |

0 |

1 |

Синхронный сброс в 0 |

TODO

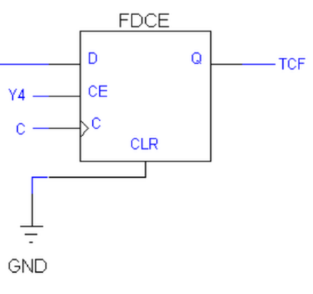

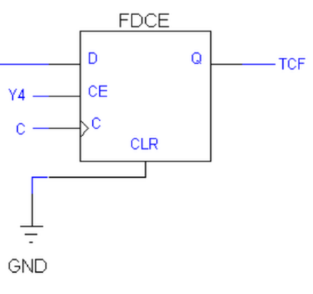

Регистр флага TCF

Отвечает за хранение значения бита операнда B на позиции A.

| Обозначение |

Назначение |

| Y8 |

| 0 |

Хранение |

| 1 |

Загрузка |

TODO

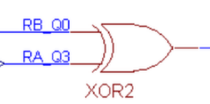

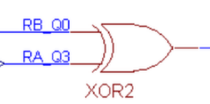

Комбинационная схема CS1

Отвечает за формирование знака произведения.

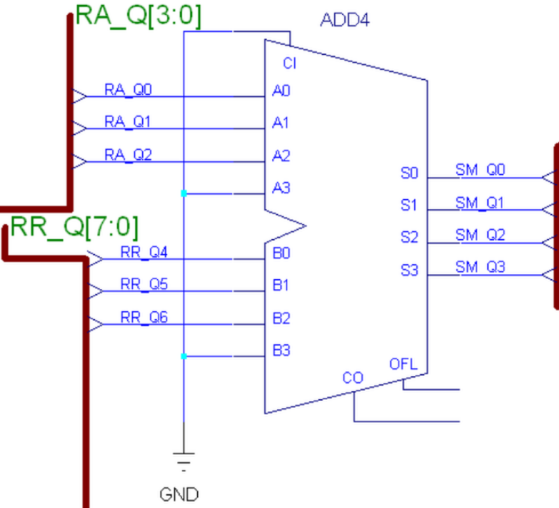

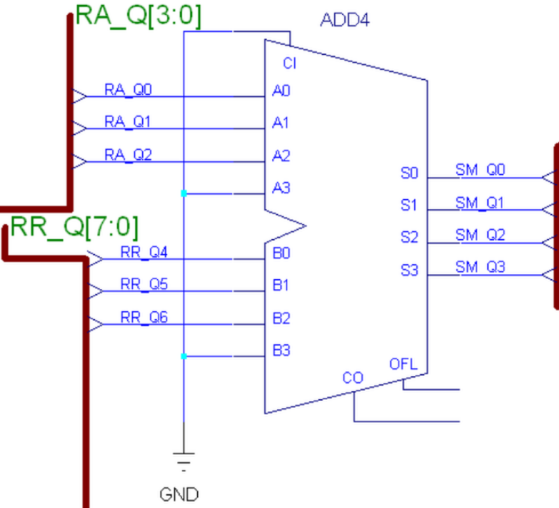

Сумматор SM

4-х битный сумматор ADD4.

TODO

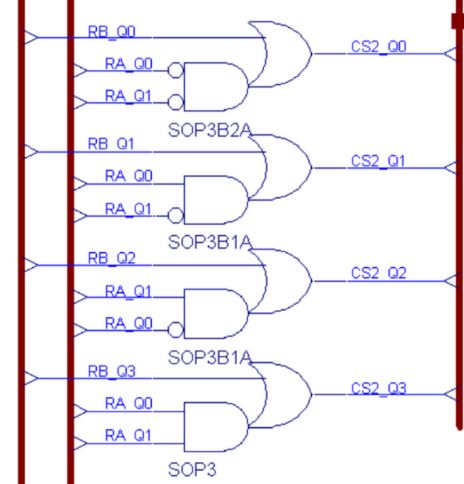

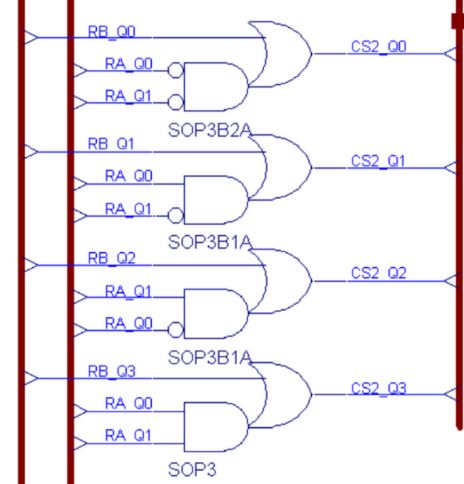

Комбинационная схема CS2

Отвечает за формирование флага CF (бита из B на позиции A).

TODO

Комбинационная схема CS3

Отвечает за формирование нового значения B с установленным битом на позиции A.

TODO

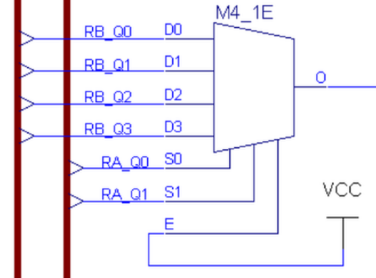

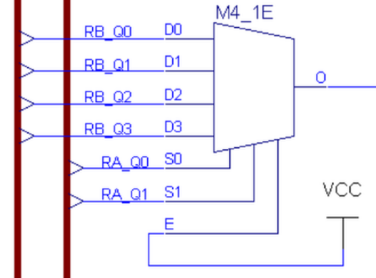

Комбинационная схема CS4

Отвечает за выбор данных для загрузки в RB: B или CS3.

TODO

Логическая схема блока операций

TODO

Микропрограммы выполнения операций

Определение сигналов блока операций

| Сигнал |

Операция |

| Y1

| Загрузка A в RA |

| Y2 |

Загрузка CS4 в RB |

| Y3 |

Логический сдвиг вправо RB |

| Y4 |

Загрузка значения на выходе SM в RR |

| Y5 |

Логический сдвиг вправо RR |

| Y6 |

Синхронный сброс RR |

| Y7 |

Вход EN для CS1 |

| Y8 |

Загрузка признака на выходе CS2 в TCF |

| Y9 |

Выбор данных для загрузки в RB: B или CS3 |

| Сигнал |

Операция |

| F1 |

Младший разряд B |

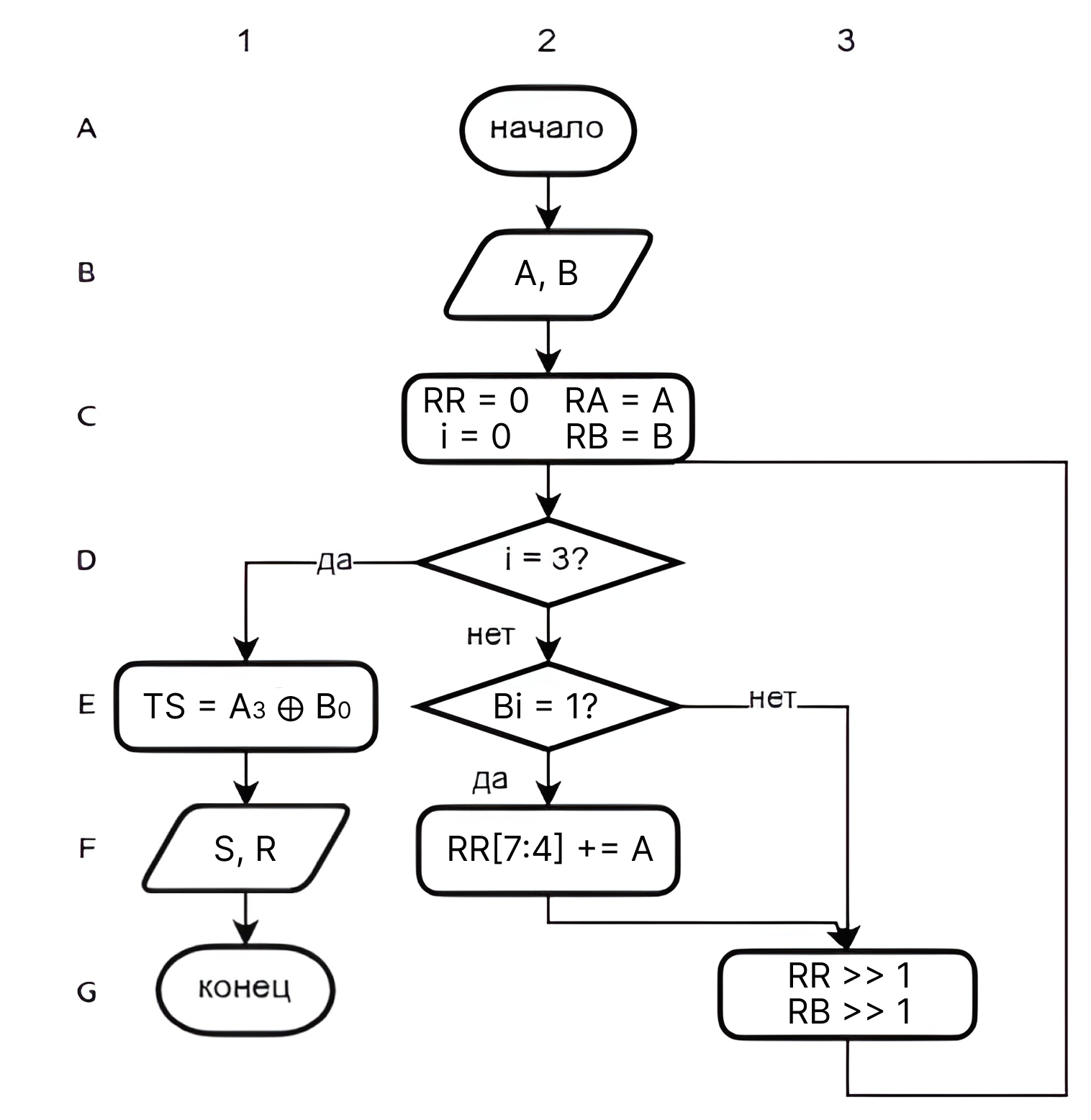

Алгоритм микропрограммы УМНОЖЕНИЕ

Примеры микропрограммы УМНОЖЕНИЕ

Пример 1 микрооперации УМНОЖЕНИЕ приведен в таблице .

TODO

Пример 2 микрооперации УМНОЖЕНИЕ приведен в таблице .

TODO

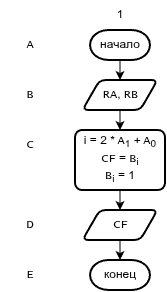

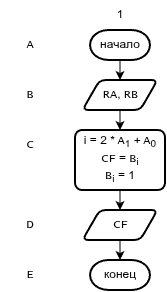

Алгоритм микрооперации УСТАНОВКА БИТА

Примеры микрооперации УСТАНОВКА БИТА

TODO

Проектирование местного устройства управления

Функциональная схема

Для реализации местного устройства управления MUU с "жёсткой" логикой разработана функциональная схема,

представленная на рисунке .

Модифицированные алгоритмы выполнения операций

Для реализации местного устройства управления алгоритмы выполнения операций должны быть изменены. На рисунках

и приведены модифицированные схемы алгоритма

микропрограмм выполнения операций УМНОЖЕНИЕ и УСТАНОВКА БИТА.

Проектирование датчика состояний

Для реализации датчика состояний необходимо по модифицированным алгоритмам выполнения операций спроектировать

граф состояний автомата датчика состояний, который будет определять логическую реализацию местного устройства

управления.

Автомат начинает свою работу с приходом сигнала SNO. В каждом состоянии

формируются определенные для этого состояния сигналы Yi и Yct для продвижения счетчика тактов CT.

После выполнения всех операций автомат переходит в начальное состояние, генерируя сигнал конца операции SKO, и

остается в этом состоянии до следующего запроса SNO.

Графы переходов автомата

В момент времени после сигнала SKO и до сигнала SNO граф находится в состоянии IDLE, при котором никакие сигналы

Y не установлены. Графы операций представлены на рисунках и .

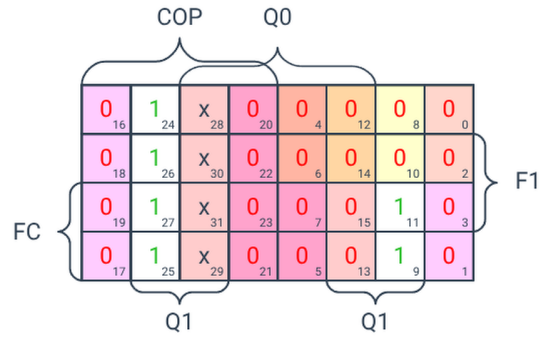

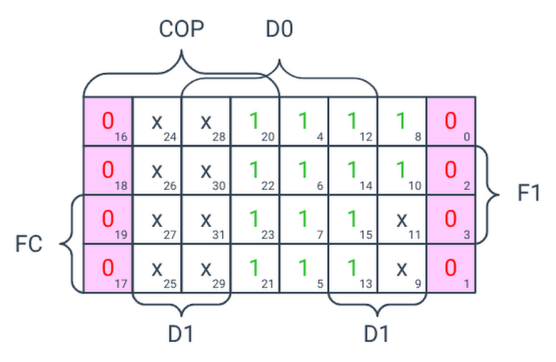

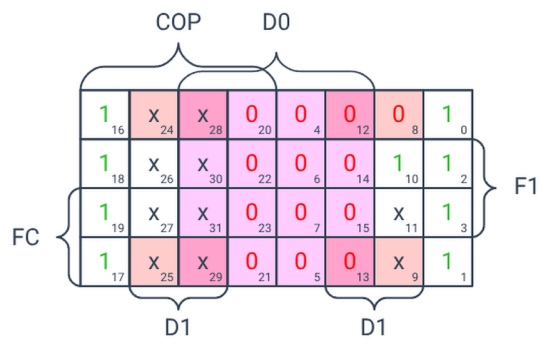

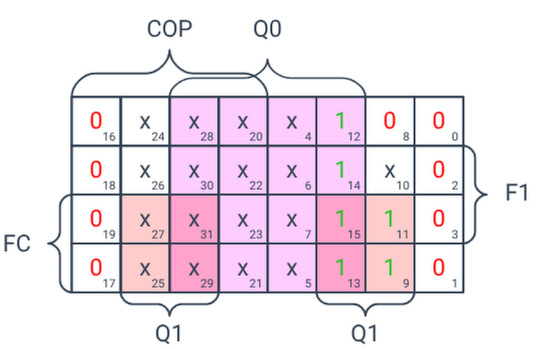

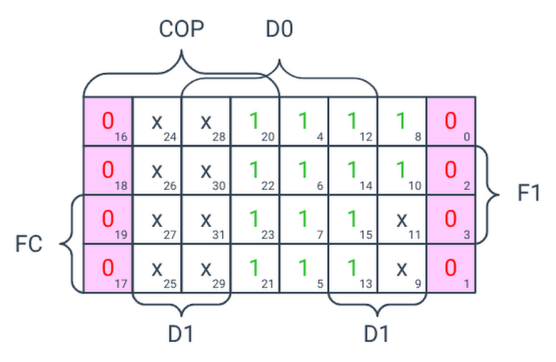

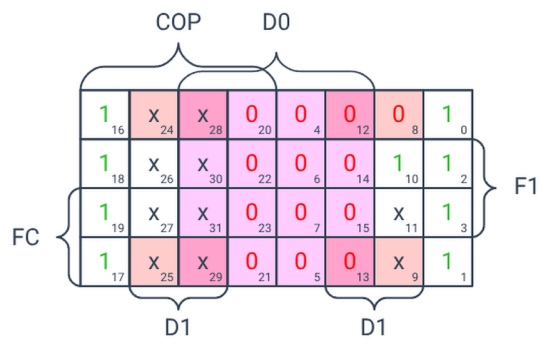

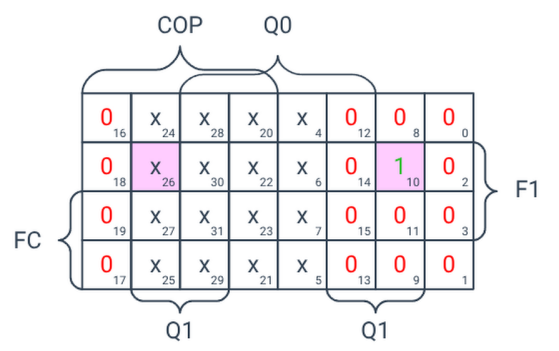

Таблица переходов DS / истинности CS1

Состояния будут храниться в 2-х битном регистре с параллельной загрузкой, состояния P1, P2, P3 соответсвуют

своим номерам в

двоичном виде, состояние IDLE = 00 - начальное. Явно возвращаться в него после формирования SKO не нужно, тк

происходит

синхронный сброс датчика состояний по сигналу SNO.

$МКНФ: Q_1 = (D_1 + D_0)$

$МКНФ: Q_0 = (\overline{D_0}) \cdot (\overline{D_1} + F_1)$

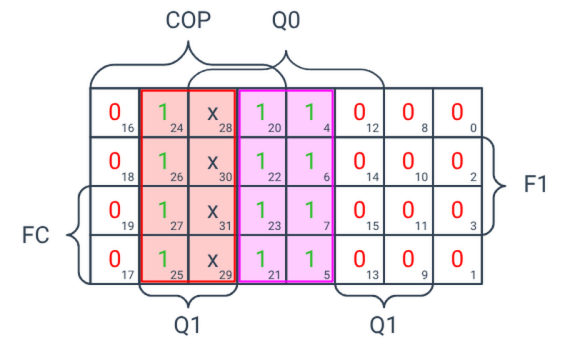

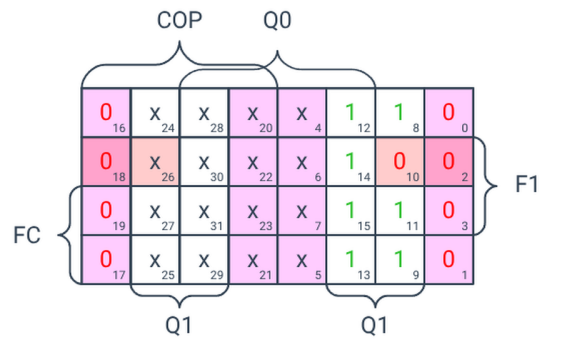

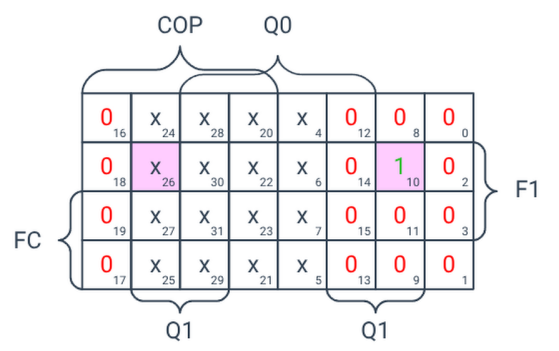

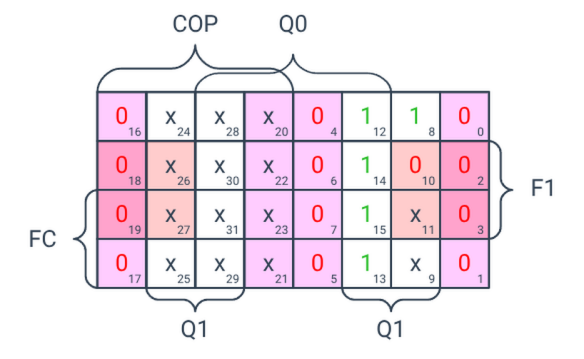

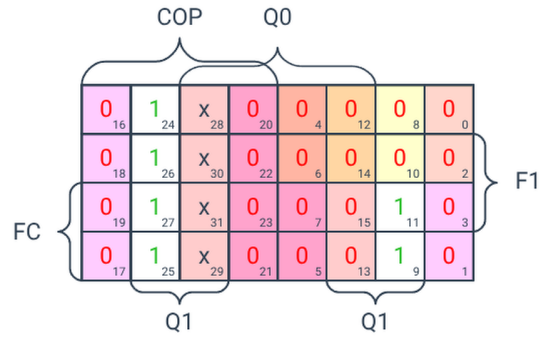

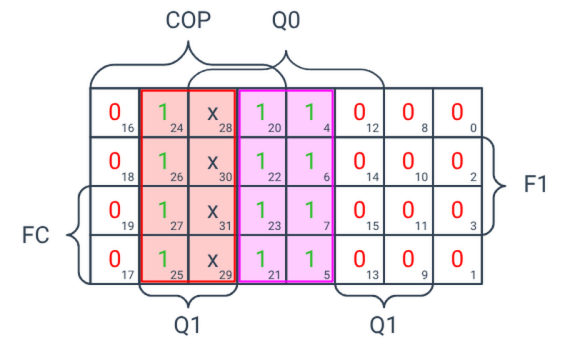

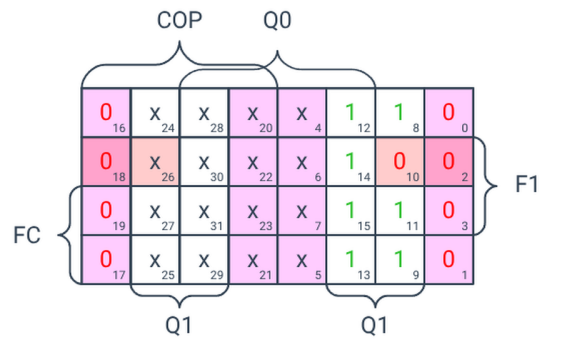

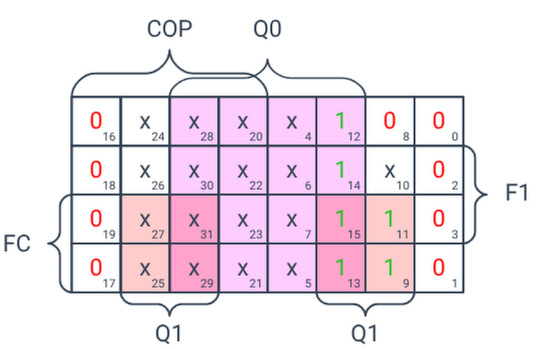

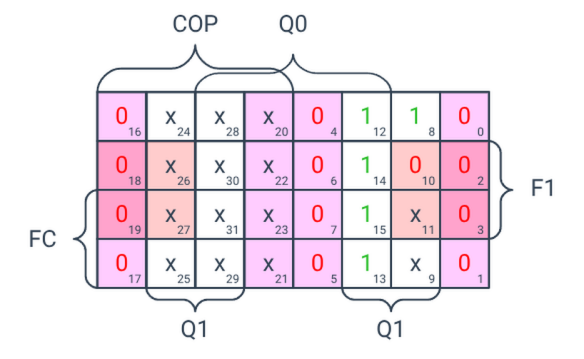

Таблица управляющих сигналов Y / истинности CS2

В таблице отражены сигналы Yi и Yct, подающиеся на выход MUU в каждом

состоянии. Часть функций являются подмножествами других функций, поэтому они минимизироватся не будут.

$Y_2 \supset Y_1,Y_6,Y_8$

$Y_3 \supset Y_5$

$Y_9 \supset Y_8$

$SKO \supset Y_8,Y_9$

$Y_1, Y_6, Y_8 := Y_2$

$Y_5 := Y_3$

$Y_9 := SKO$

$МДНФ: Y_2 = \overline{Q_1} \cdot Q_0 + COP \cdot Q_1$

$МКНФ: Y_3 = (Q_1) \cdot (Q_0 + \overline{F_1} + FC)$

$МДНФ: Y_4 = Q_1 \cdot \overline{Q_0} \cdot F_1 \cdot \overline{FC}$

$МДНФ: Y_7 = Q_0 + Q_1 \cdot FC$

$МКНФ: Y_{ct} = (Q_1) \cdot (Q_0 + \overline{F_1})$

$МКНФ: SKO = (Q_1) \cdot (\overline{Q_0}) \cdot (COP + FC)$