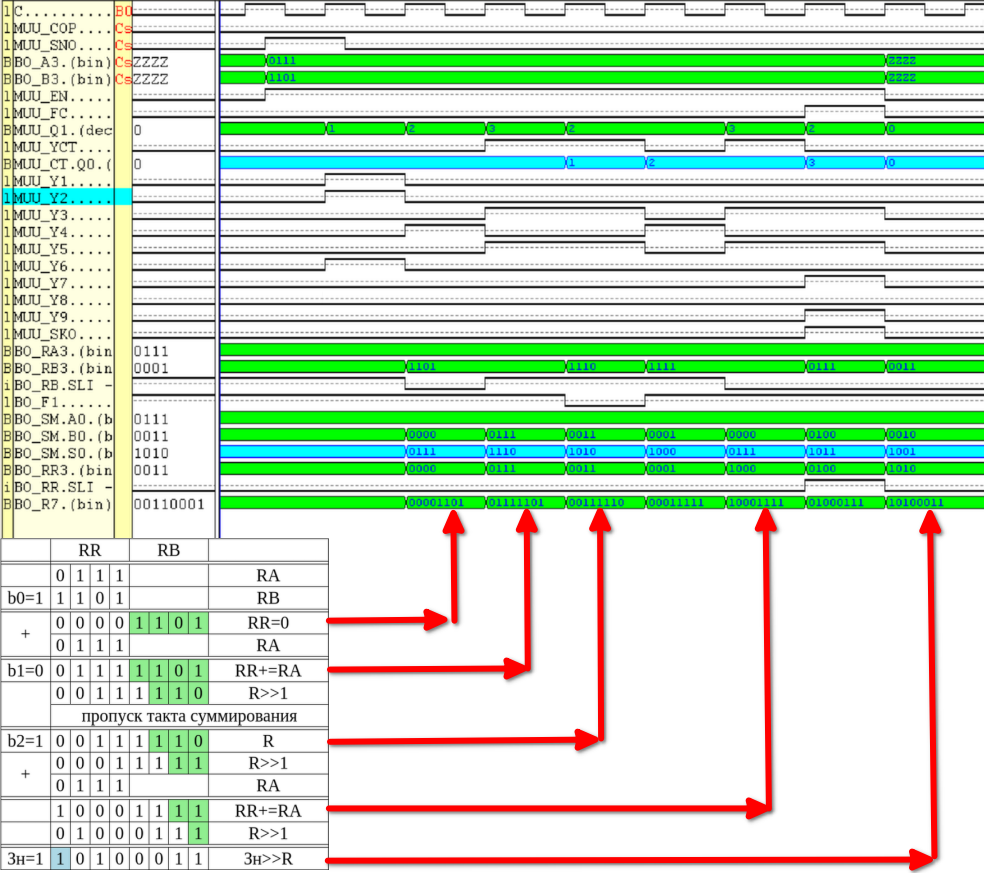

Рассмотренный алгоритм умножения представлен на рисунке .

Проверка бита с установкой его в единицу

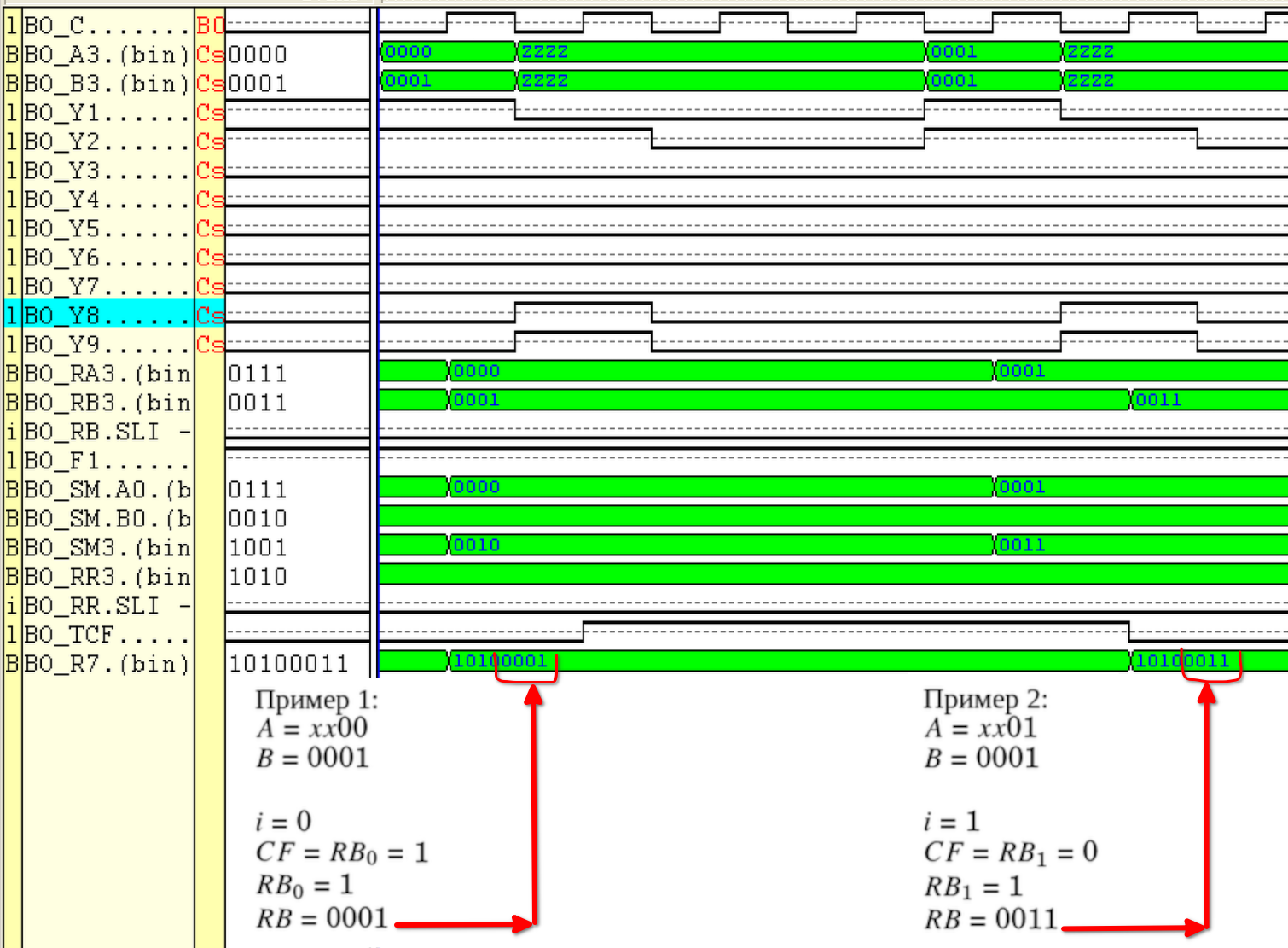

Операция проверяет бит в RB на позиции RA, устанавливает флаг CF, если значение бита в операнде 1, значение бита в операнде устанавливается в 1.

4-х разрядное слово представлено целыми числами с фиксированной запятой в прямом коде. Старший разряд отводится под знак числа. Результат операции умножение - двойное слово, операции установки бита - одинарное слово.

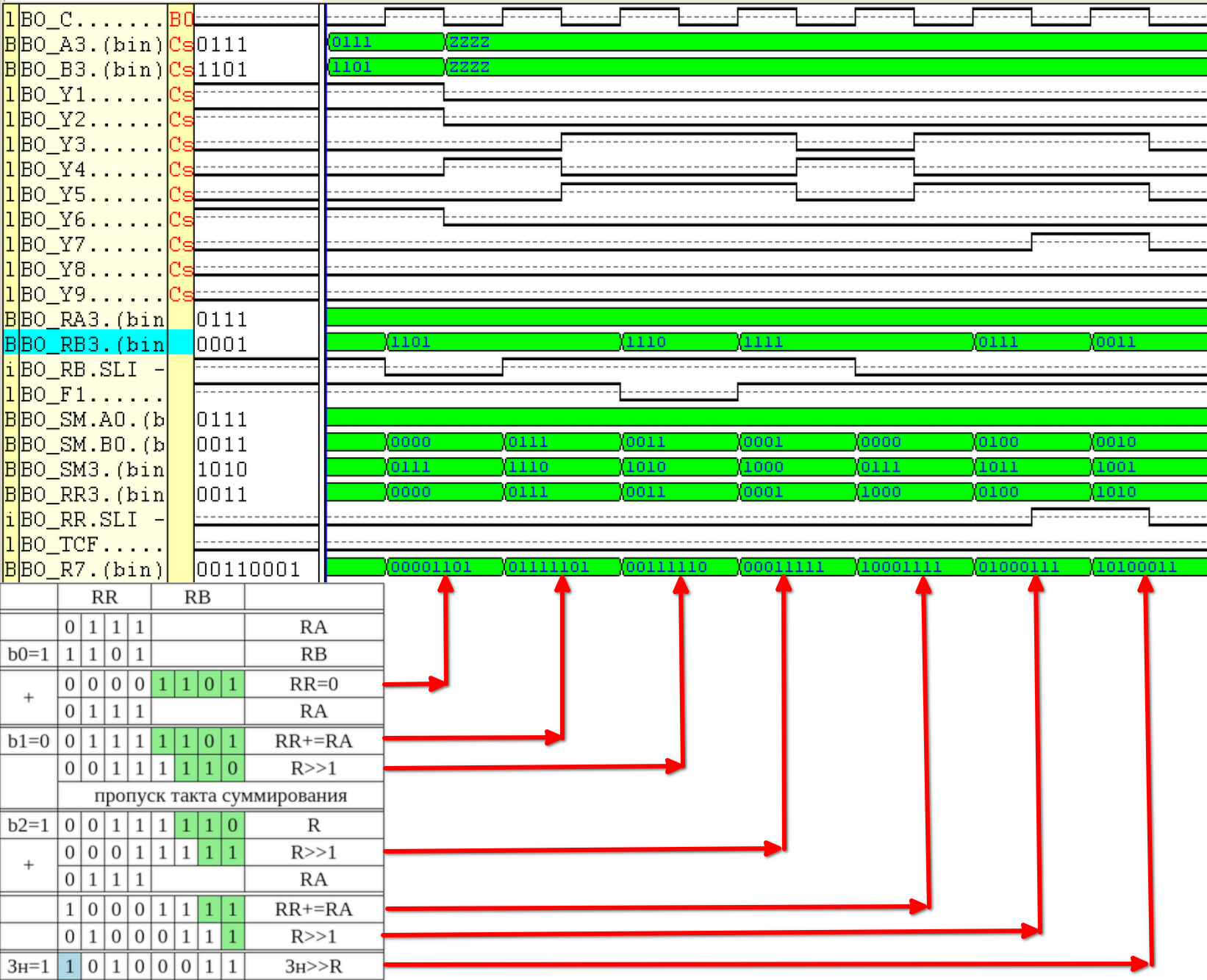

$$[A]_{\text{п}} = a_3, a_2 a_1 a_0$$ $$[R]_{\text{п}} = r_7, r_6 r_5 r_4 r_3 r_2 r_1 r_0$$Умножение выполняется по алгоритму умножения с младших разрядов множителя и сдвигом суммы частичных произведений вправо с одним корректирующим шагом. Данный алгоритм при представлении сомножителей в прямом коде можно выразить следующей формулой:

Рассмотренный алгоритм умножения представлен на рисунке .

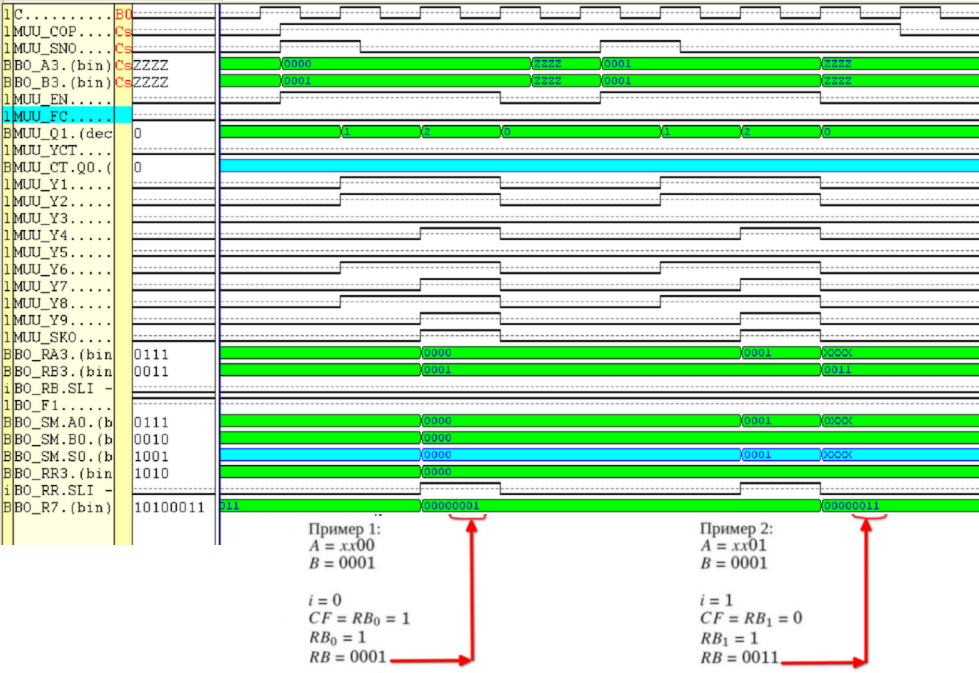

Операция проверяет бит в RB на позиции RA, устанавливает флаг CF, если значение бита в операнде 1, значение бита в операнде устанавливается в 1.

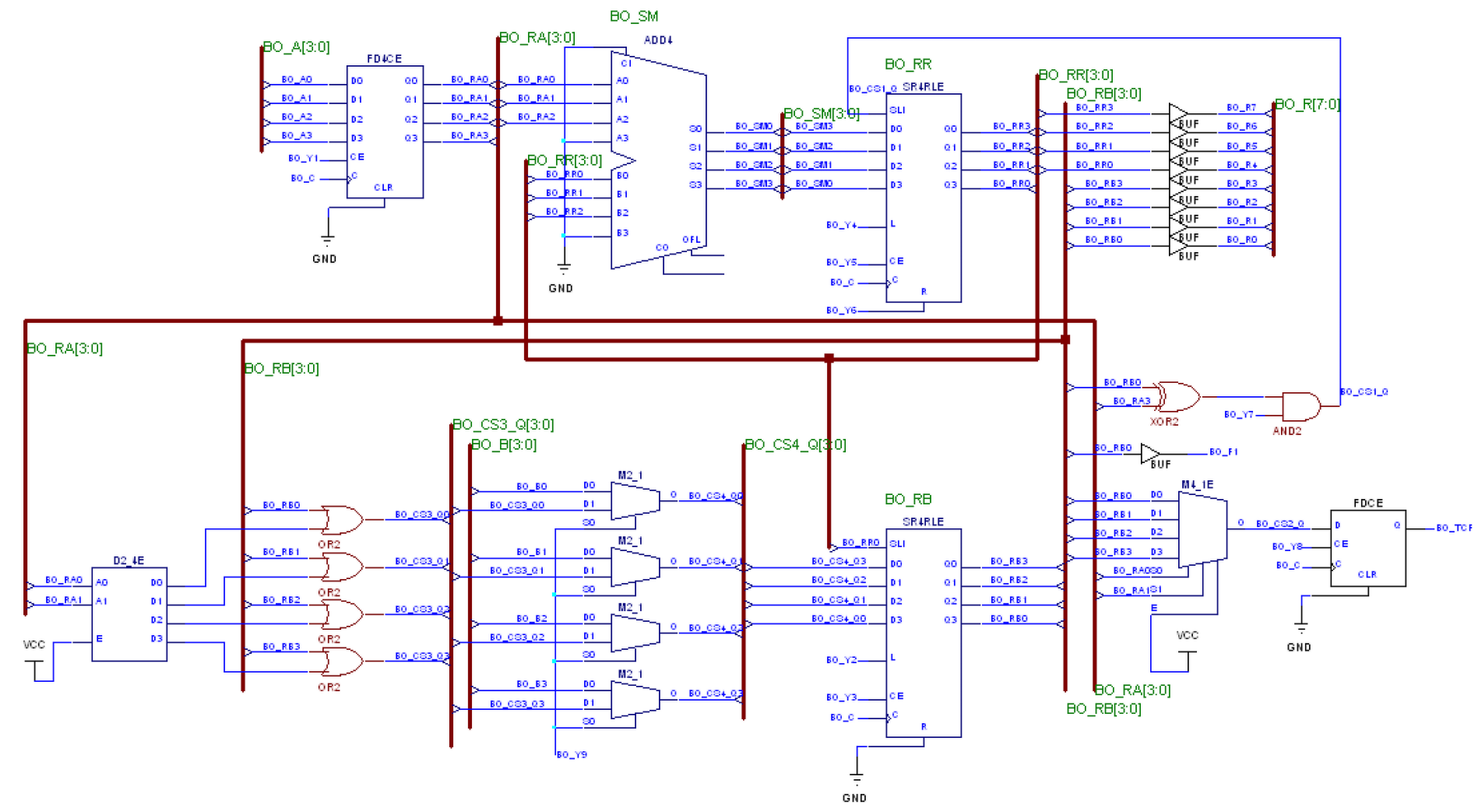

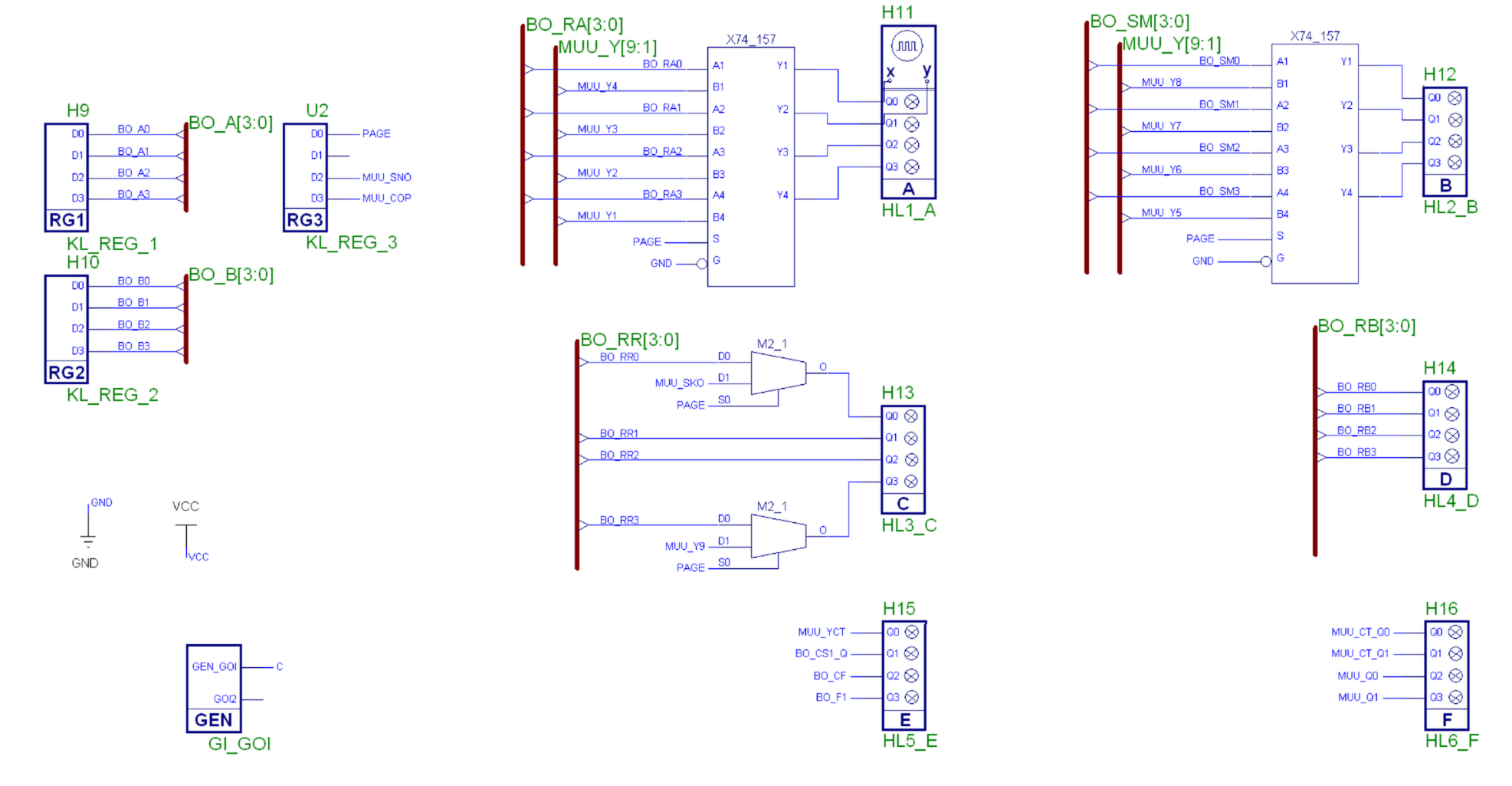

Функциональная схема блока операций представлена на рисунке , в таблице приведены все элементы функциональной схемы блока операций с их функциями и назначением.

| Обозначение блока | Назначение |

|---|---|

| RA | Регистр первого операнда, 4 разряда, хранение, параллельная загрузка A |

| RB | Регистр второго операнда / младшей части результата, 4 разряда, хранение, параллельная загрузка B, логический сдвиг вправо, формирование сигнала F0 |

| RR | Регистр старшей части результата, 4 разряда, хранение, параллельная загрузка, логический сдвиг вправо с переносом в RB, синхронный сброс в 0 |

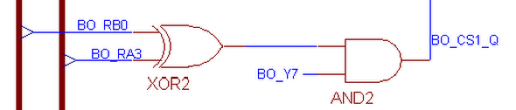

| CS1 | Формирование знака произведения |

| CS2 | Формирование флага CF (значения бита из B на позиции A) |

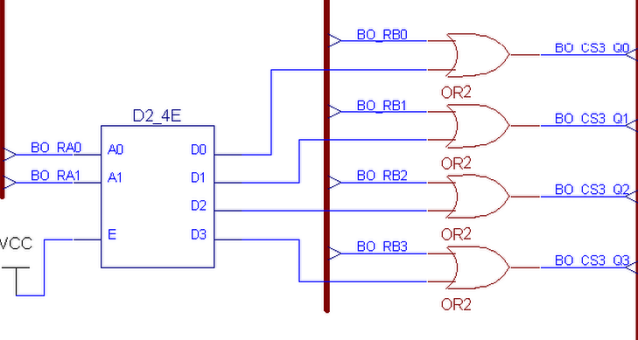

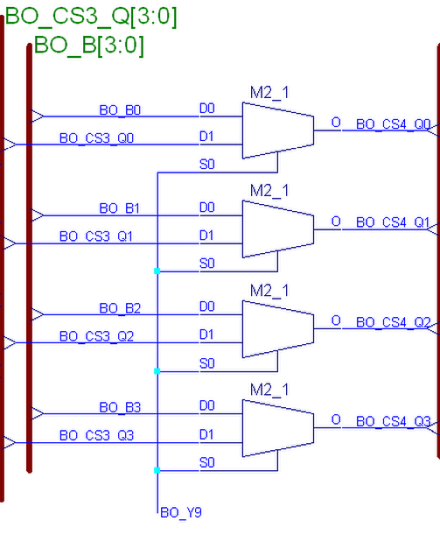

| CS3 | Формирование нового значения B с установленным битом на позиции A |

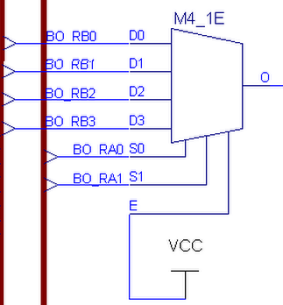

| CS4 | Выбор данных для загрузки в RB: B или CS3 |

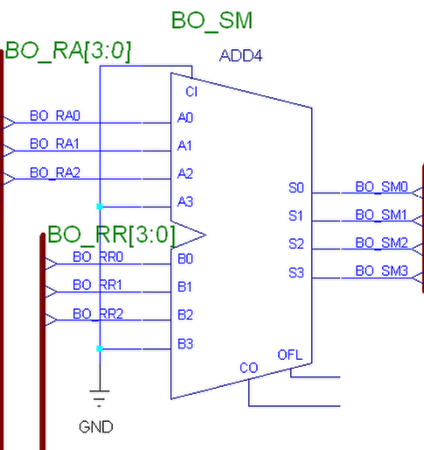

| SM | Сумматор, 4 разряда |

| TCF | Регистр флага CF (значения бита из B на позиции A), 1 разряд, хранение, загрузка |

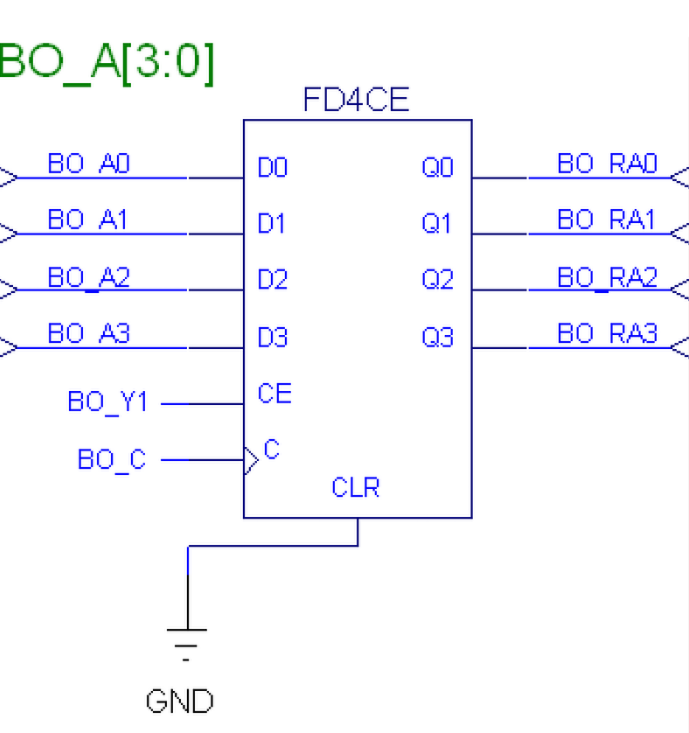

Данный регистр является четырёхразрядным регистром хранения. Наиболее подходящим для реализации функций регистра RA является регистр FD4CE.

| Обозначение | Назначение |

|---|---|

| Y1 | |

| 0 | Хранение |

| 1 | Параллельная загрузка |

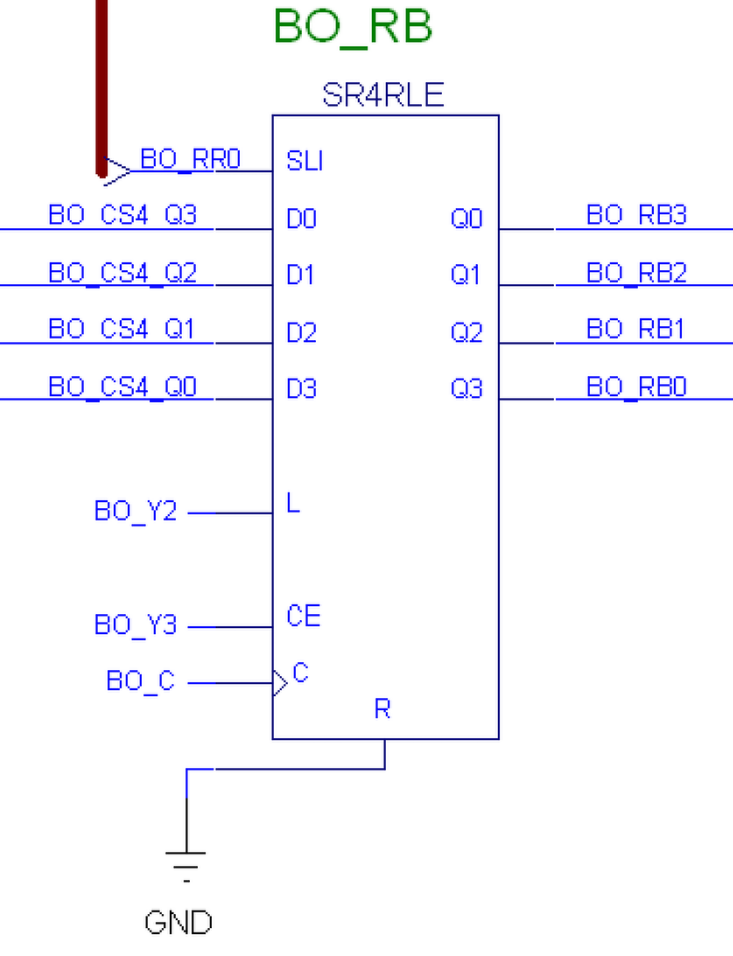

Данный регистр должен выполнять микрооперации хранения, параллельной загрузки и логического сдвига вправо (с заполнением старшего бита младшим разрядом из RR). Для реализации выбран универсальный сдвиговый регистр SR4CLE. Младший бит выхода RB_Q0 формирует сигнал F0.

| Обозначение | Назначение | |

|---|---|---|

| Y2 | Y3 | |

| 0 | 0 | Хранение |

| 1 | x | Параллельная загрузка |

| 0 | 1 | Логический сдвиг вправо |

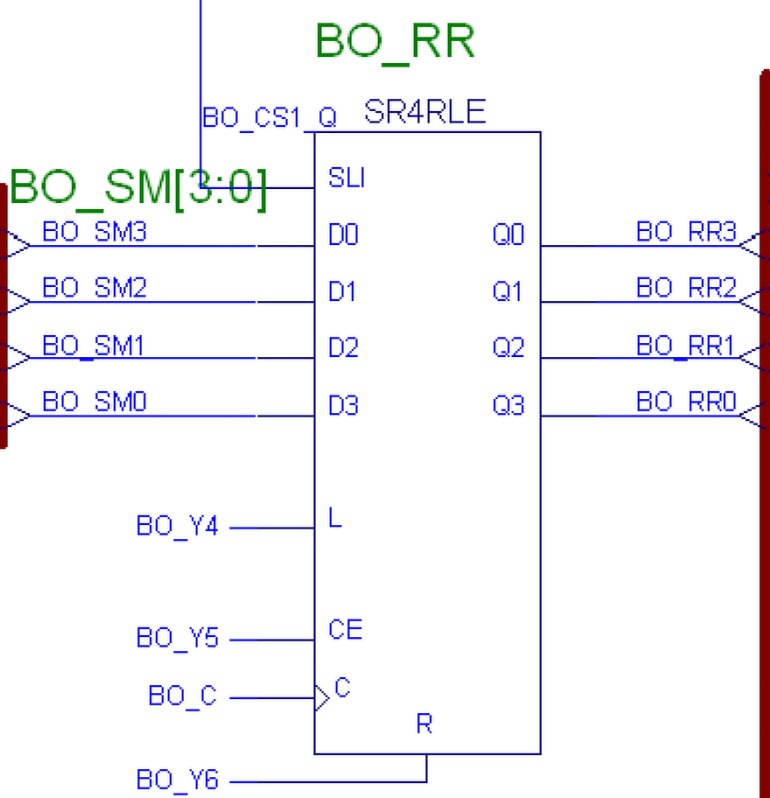

Данный регистр должен выполнять микрооперации хранения, параллельной загрузки, логического сдвига вправо (c коммутацией младшего бита в старший разряд RB) и синхронного сброса в 0. Для реализации выбран универсальный сдвиговый регистр SR4RLE.

| Обозначение | Назначение | ||

|---|---|---|---|

| Y4 | Y5 | Y6 | |

| 0 | 0 | 0 | Хранение |

| 1 | x | 0 | Параллельная загрузка |

| 0 | 1 | 0 | Логический сдвиг вправо |

| x | x | 1 | Синхронный сброс в 0 |

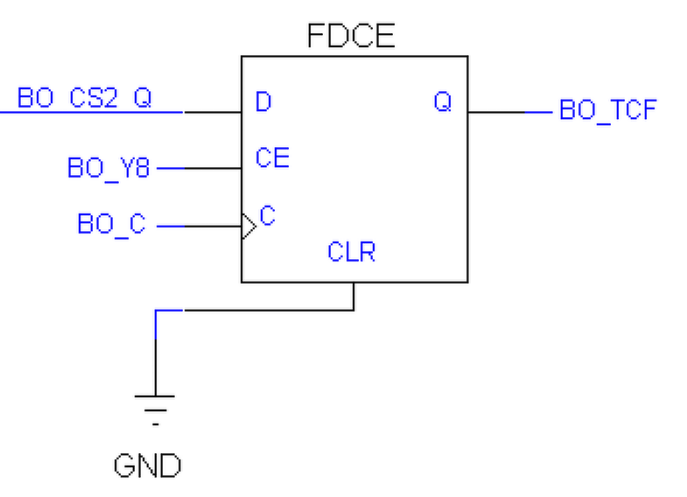

Отвечает за хранение значения бита операнда B на позиции A.

| Обозначение | Назначение |

|---|---|

| Y8 | |

| 0 | Хранение |

| 1 | Загрузка |

Отвечает за формирование знака произведения.

4-х битный сумматор ADD4.

Отвечает за формирование флага CF (бита из B на позиции A).

Отвечает за формирование нового значения B с установленным битом на позиции A.

Отвечает за выбор данных для загрузки в RB: B или CS3.

| Сигнал | Операция |

|---|---|

| Y1 | Загрузка A в RA |

| Y2 | Загрузка CS4 в RB |

| Y3 | Логический сдвиг вправо RB |

| Y4 | Загрузка значения на выходе SM в RR |

| Y5 | Логический сдвиг вправо RR |

| Y6 | Синхронный сброс RR |

| Y7 | Вход EN для CS1 |

| Y8 | Загрузка признака на выходе CS2 в TCF |

| Y9 | Выбор данных для загрузки в RB: B или CS3 |

| Сигнал | Операция |

|---|---|

| F1 | Младший разряд B |

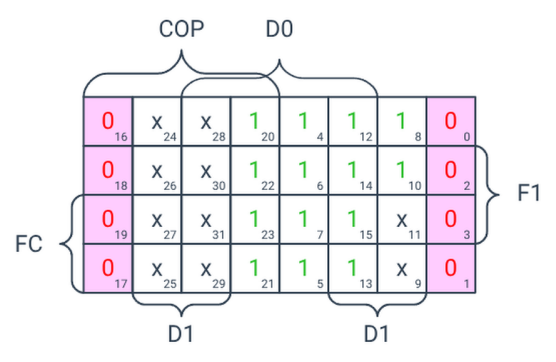

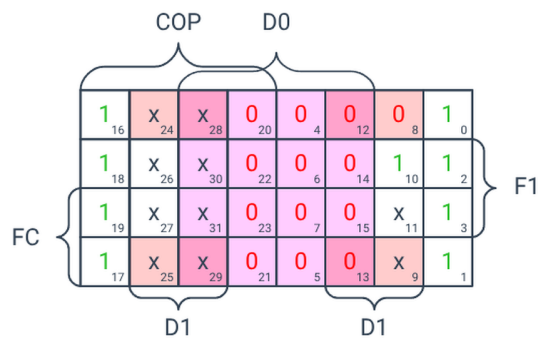

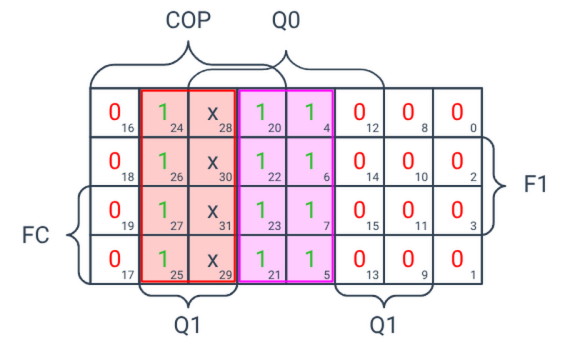

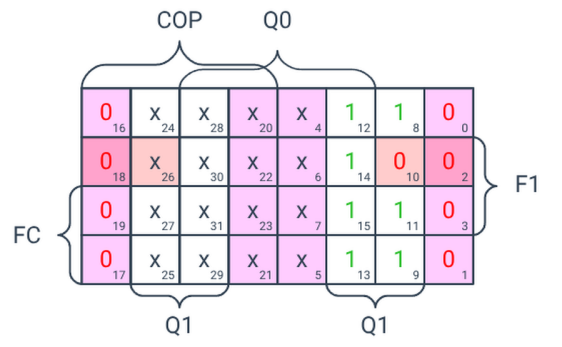

Пример 1 микрооперации УМНОЖЕНИЕ приведен в таблице .

Пример 2 микрооперации УМНОЖЕНИЕ приведен в таблице .

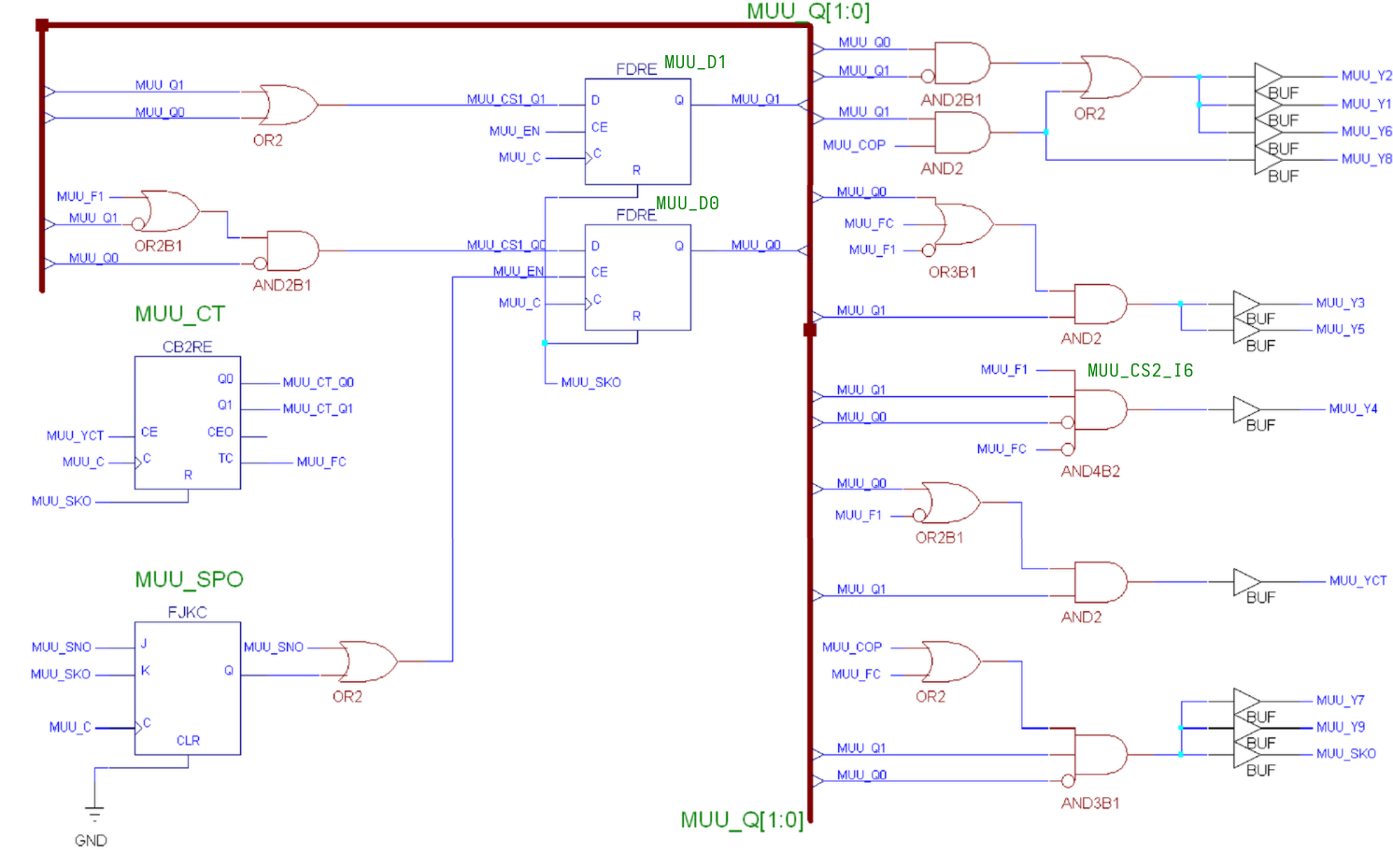

Для реализации местного устройства управления MUU с "жёсткой" логикой разработана функциональная схема, представленная на рисунке .

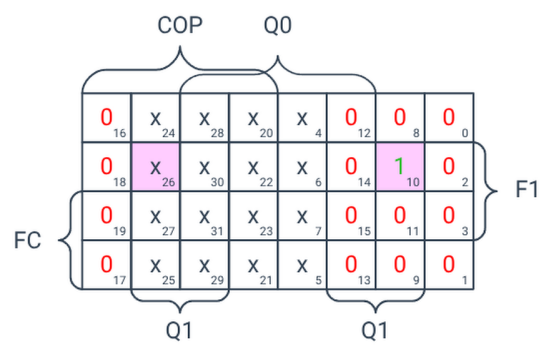

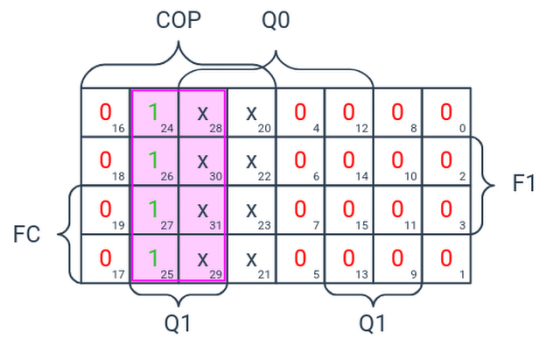

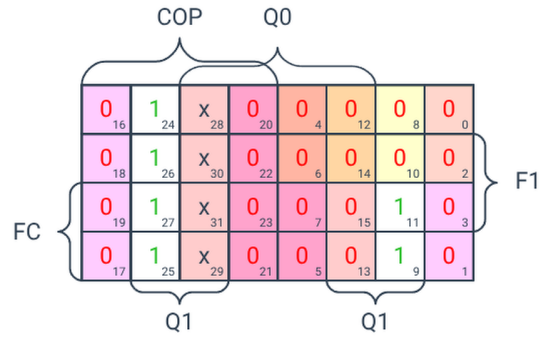

Для реализации местного устройства управления алгоритмы выполнения операций должны быть изменены. На рисунках и приведены модифицированные схемы алгоритма микропрограмм выполнения операций УМНОЖЕНИЕ и УСТАНОВКА БИТА.

Для реализации датчика состояний необходимо по модифицированным алгоритмам выполнения операций спроектировать граф состояний автомата датчика состояний, который будет определять логическую реализацию местного устройства управления.

Автомат начинает свою работу с приходом сигнала SNO. В каждом состоянии формируются определенные для этого состояния сигналы Yi и Yct для продвижения счетчика тактов CT.

После выполнения всех операций автомат переходит в начальное состояние, генерируя сигнал конца операции SKO, и остается в этом состоянии до следующего запроса SNO.

В момент времени после сигнала SKO и до сигнала SNO граф находится в состоянии IDLE, при котором никакие сигналы Y не установлены. Графы операций представлены на рисунках и .

Состояния будут храниться в 2-х битном регистре с параллельной загрузкой, состояния P1, P2, P3 соответсвуют своим номерам в двоичном виде, состояние IDLE = 00 - начальное. Явно возвращаться в него после формирования SKO не нужно, тк происходит синхронный сброс датчика состояний по сигналу SKO.

В таблице отражены сигналы Yi и Yct, подающиеся на выход MUU в каждом состоянии. Часть функций являются подмножествами других функций, поэтому они минимизироватся не будут.

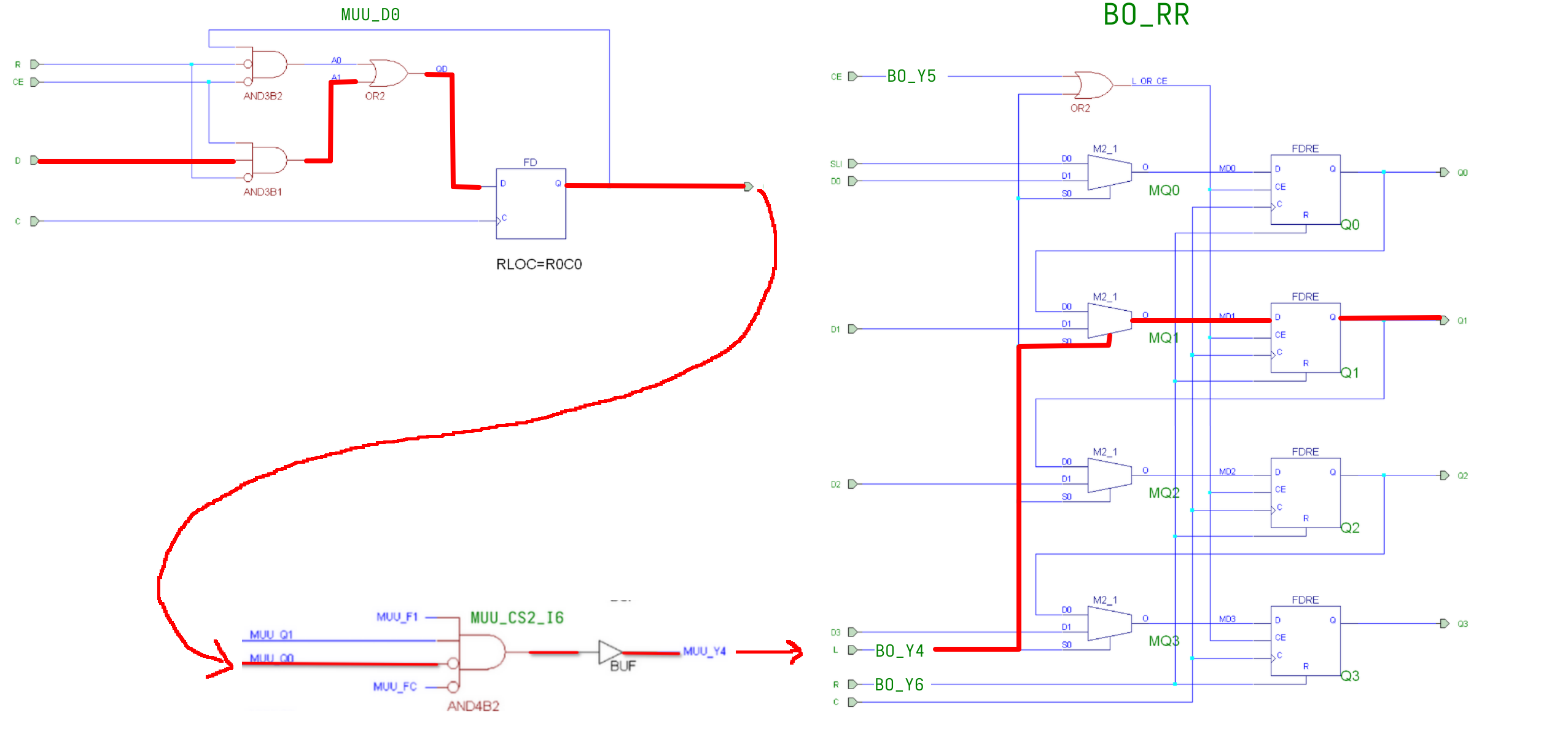

На рисунке представлена синтезированная логическая схема местного устройства управления.

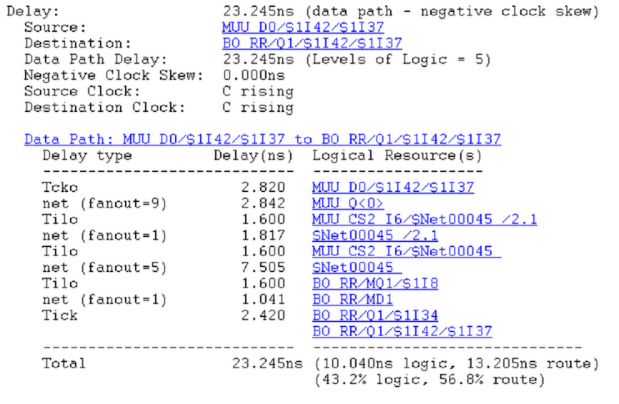

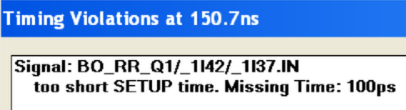

Получен отчет статического анализа времени предварительной установки с помощью программы "Timing Analyzer", который представлен на рисунке . На рисунке представлено внутреннее устройство схем, участвующих в критическом пути сигнала.

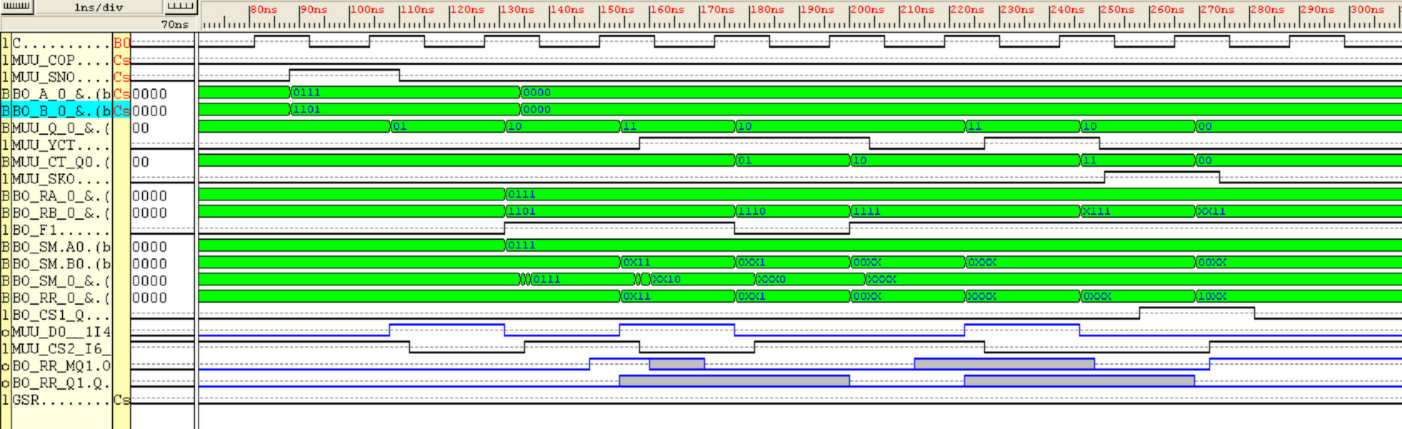

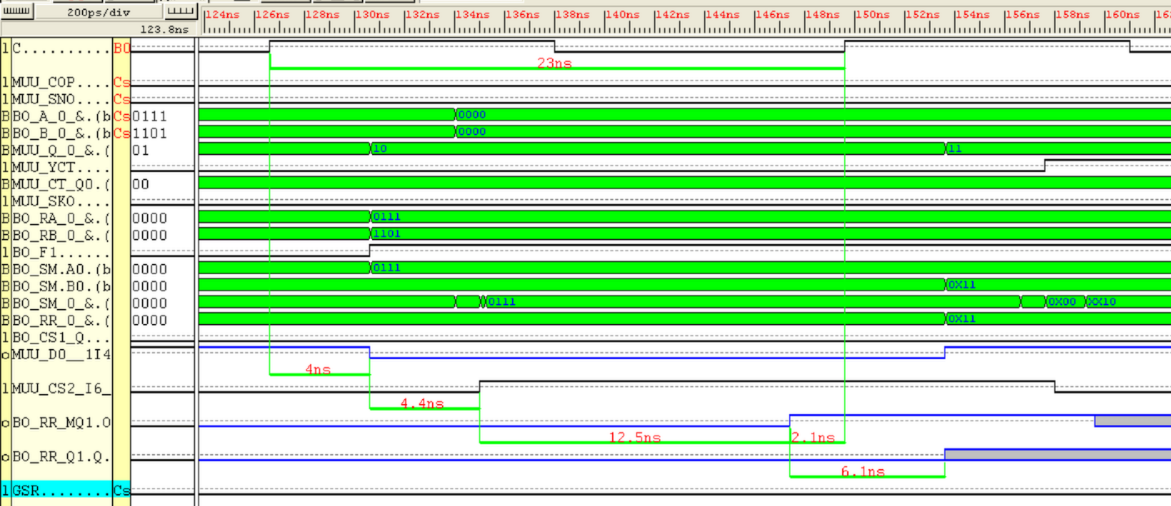

Используя результат работы "Timing Analyzer" как отправную точку, в режиме временного моделирования был определен минимальный период сихнроимпульсов 23.2ns, не вызывающий состязаний. На рисунке представлена временная диаграмма с путем сигнала, на рисунке представлены измерения задержек сигнала.

Длительность критического пути операции УМНОЖЕНИЕ:

4(MUU_Q0) + 4.4(MUU_Y4) + 12.5(BO_RR_D1) + 2.1(tуст BO_RR_Q1) = 23ns.

В таблице приведены параметры быстродействия АЛУ.

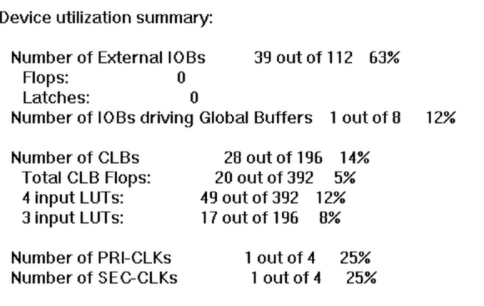

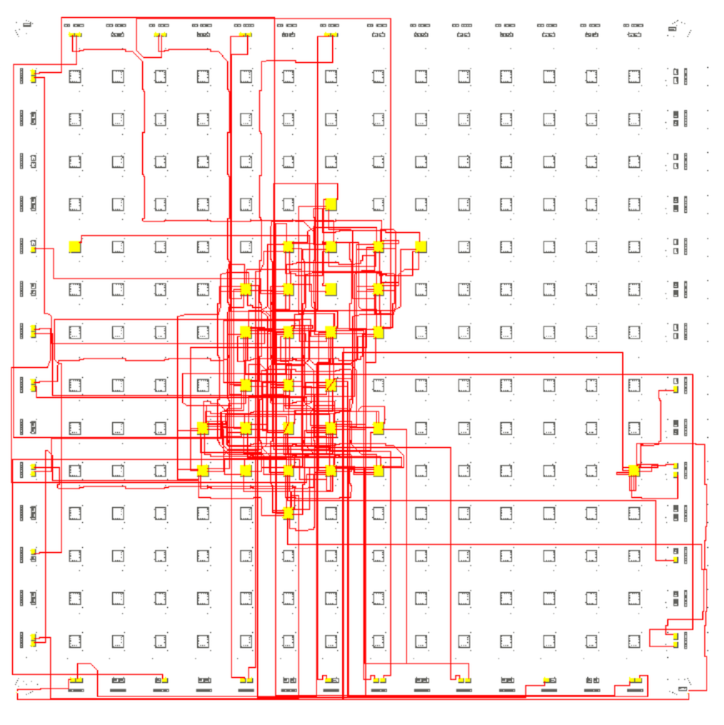

Для подключения АЛУ к стэнду задействовано количество элементов, приведенное на рисунке . На рисунке представлена схема размещения элементов на кристалле ПЛИС.

Схема управления АЛУ на стенде представлена в таблице и на рисунке .

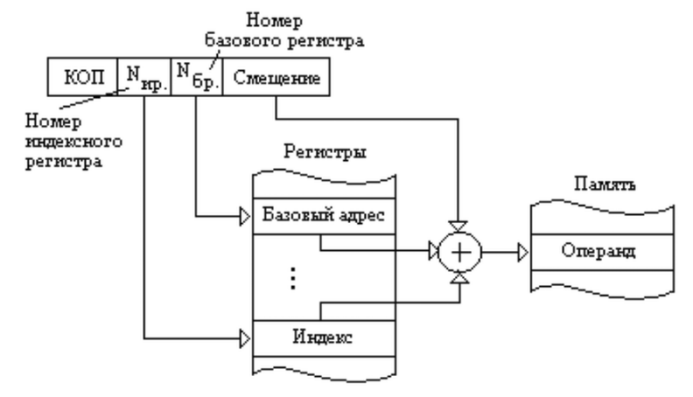

Оперативная память имеет организацию 16x8 ячеек, регистровая - 8x4. В каждой ячейке ОП хранится два четырехразрядных слова, каждое из которого имеет свой адрес. Четыре старших разряда логического адреса ячейки являются физическим адресом, младший бит логического адреса указывает на старший/младший полубайт. В таблице представлена схема адресации оперативной памяти.

Под адрес ОП выделяется 5 бит, под адрес РП выделяется 3 бита, в первой половине ячеек ОП содержатся команды, во второй операнды, поэтому исполнительный адрес 4 бита.

Длинные слова хранятся в формате Little Endian.

ЛИНЕЙНАЯ команда - два слова, двухадресная, формат регистр-память. Первый операнд в РП указывается с помощью прямой адресации, второй операнд в ОП с помощью базовой с индексированием адресации вар. 1. Результат УМНОЖЕНИЯ по адресу второго операнда, результат УСТАНОВКИ БИТА по адресу первого операнда.

Команда ПЕРЕХОДА - одно слово, одноадресная. Адрес перехода указывается с помощью относительной адресации со знаком в дополнительном коде. Условный переход осуществляется, если значение флага CF = 1.

Линейные команды состоят из 4-х слов, нелинейные из 2-х, поэтому всегда, независимо от команды, считывается 2 слова, а затем, если команда линейная, считывается еще 2 слова. Алгоритм выполнения команды представлен на рисунке .

Функциональная схема БУК представлена на рисунке X, в таблице X приведены все элементы функциональной схемы БУК с их функциями и назначением.